Power management capabilities (pmc) – Avago Technologies LSI53C896 User Manual

Page 129

PCI Configuration Registers

4-17

Version 3.3

Copyright © 1998–2003 by LSI Logic Corporation. All rights reserved.

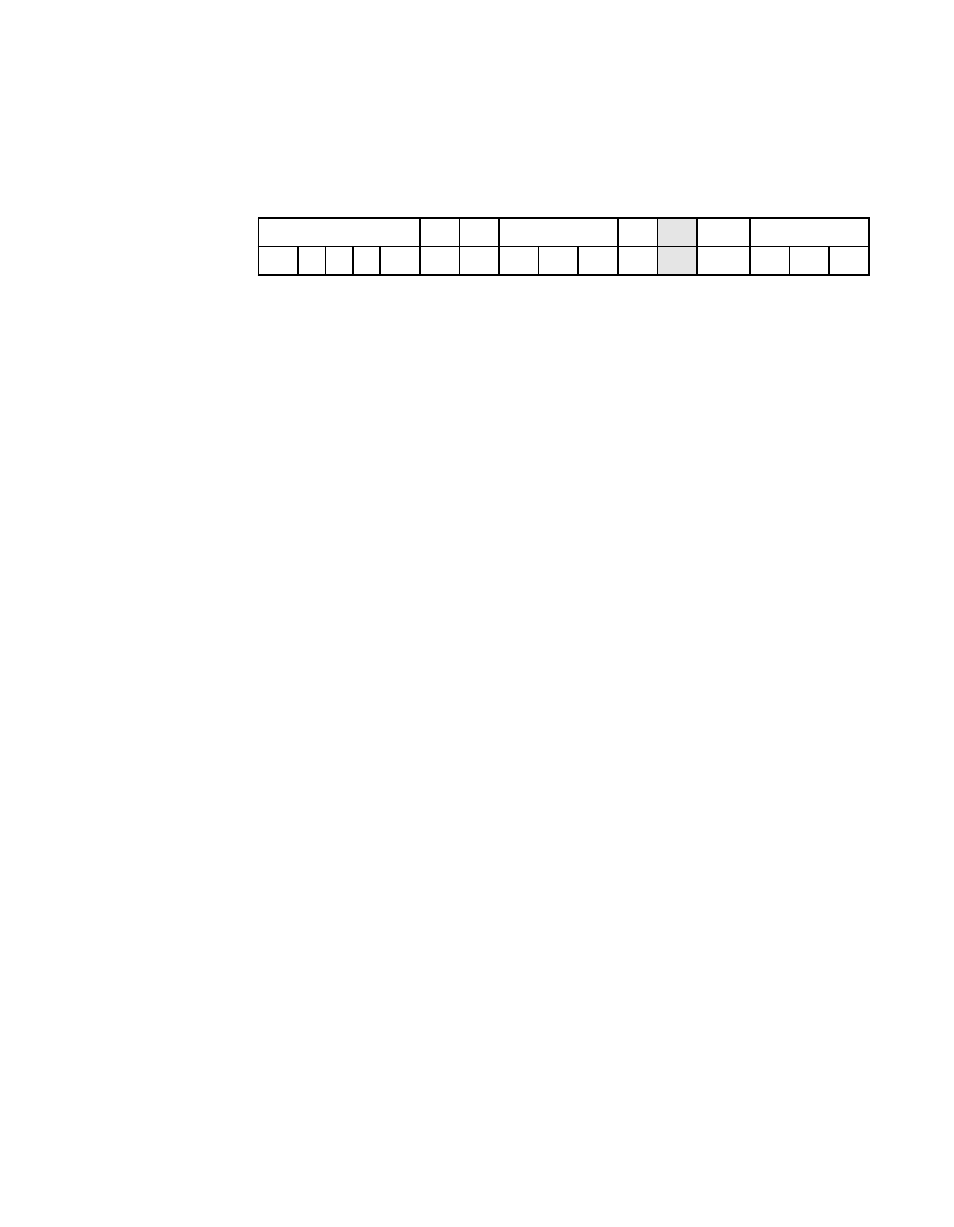

Registers: 0x42–0x43

Power Management Capabilities (PMC)

Read Only

PMES

PME_Support

[15:11]

Bits [15:11] define the power management states in

which the LSI53C896 asserts the PME pin. These bits

are all set to zero because the LSI53C896 does not

provide a PME signal.

D2S

D2_Support

10

The LSI53C896 sets this bit to indicate support for power

management state D2.

D1S

D1_Support

9

The LSI53C896 sets this bit to indicate support for power

management state D1.

AUXC

Aux_Current

[8:6]

The LSI53C896 always returns zeros. This feature is not

supported.

DSI

Device Specific Initialization

5

This bit is cleared to indicate that the LSI53C896 requires

no special initialization before the generic class device

driver is able to use it.

R

Reserved

4

PMEC

PME Clock

3

Bit 3 is cleared because the LSI53C896 does not provide

a PME pin.

VER[2:0]

Version

[2:0]

These three bits are set to 0b010 to indicate that the

LSI53C896 complies with Revision 1.1 of the PCI Power

Management Interface Specification.

15

11

10

9

8

6

5

4

3

2

0

PMES

D2S D1S

AUXC

DSI

R

PMEC

VER[2:0]

0

0

0

0

0

1

1

0

0

0

0

0

0

0

1

0