3 j1850 vpw valid/invalid bits & symbols, J1850 vpw valid/invalid bits & symbols -19, Section 20.8.1.3, j1850 vpw valid/invalid bits – Freescale Semiconductor MPC5200B User Manual

Page 698: Symbols

Functional Description

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

20-19

The SOF symbol is defined as passive to active transition followed by an active period 200

µs in length (

(c)). This allows

the data bytes which follow the SOF symbol to begin with a passive bit, regardless of whether it is a logic one or a logic zero.

•

EOD - End of Data Symbol

The EOD symbol is defined as an active to passive transition followed by a passive period 200

µs in length (

(d)).

•

EOF - End of Frame Symbol

The EOF symbol is defined as an active to passive transition followed by a passive period 280

µs in length (

(e)). If there

is no IFR byte transmitted after an EOD symbol is transmitted, after another 80

µs the EOD becomes an EOF, indicating the

completion of the message.

•

IFS - Inter-Frame Separation Symbol

The IFS symbol is defined as a passive period 300

µs in length. The IFS symbol contains no transition, since when used it always

follows an EOF symbol.(

(g))

•

BREAK - Break Signal

The BREAK signal is defined as a passive to active transition followed by an active period of at least 240

µs (

(f)).

•

IDLE

An IDLE is defined as a passive period greater than 300

µs in length.

20.8.1.3

J1850 VPW Valid/Invalid Bits & Symbols

The timing tolerances for receiving data bits and symbols from the J1850 bus have been defined to allow for variations in oscillator

frequencies. In many cases the maximum time allowed to define a data bit or symbol is equal to the minimum time allowed to define another

data bit or symbol.

Since the minimum resolution of the BDLC module for determining what symbol is being received is equal to a single period of the MUX

Interface clock, (t

bdlc

). i.e. the receiver symbol timing boundaries are subject to an uncertainty of 1 t

bdlc

due to sampling considerations.

This clock resolution of 1 t

bdlc

allows the BDLC module to properly differentiate between the different bits and symbols, without reducing

the valid window for receiving bits and symbols from transmitters onto the J1850 bus having varying oscillator frequencies.

•

Transmit and Receive Symbol Timing Specifications

contain the SAE J1850 transmit and receive symbol timing specifications for the BDLC module.

The units used in these tables are mux interface clock periods (t

bdlc

). The mux interface clock is a divided down version of the bus

clock input to the module (see

Section 20.7.3.6, BDLC Rate Select Register (DLCBRSR) - MBAR + 0x1309

). The mux interface

clock drives the transmit and receive counters which control symbol generation and identification. The symbol timing in effect

during J1850 operations is dependent the state of two control bits: the CLKS bit BDLC Control Register 1, which indicates whether

the bus clock is an integer frequency or a binary frequency; the 4XE bit in BDLC Control Register 2, which is used to select 4X

operation.

and

indicate the transmit and receive timing for integer bus frequencies (CLKS = 0) and 4X operation disabled (4XE

= 0). It is assumed that for integer bus frequencies the divided down mux interface clock frequency will be 1MHz (t

bdlc

= 1

µs).

and

indicated the transmit and receive timing for binary bus frequencies (CLKS = 1) and 4X operation disabled (4XE

= 0). It is assumed that for binary bus frequencies the divided down mux interface clock frequency will be 1.048576 MHz (t

bdlc

= 0.953674

µs). The symbol timing values are adjusted to compensate for the shortening of the mux interface clock period.

and

show how the receive symbol timing values are adjusted when 4X operation is enabled (4XE = 1) for both integer

bus frequencies (CLKS = 0) and binary bus frequencies (CLKS = 1), respectively.

The values specified in the tables are for the symbols appearing on the SAE J1850 bus. These values assume the BDLC module is

communicating on the SAE J1850 bus using an external analog transceiver, and that the BDLC module analog roundtrip delay value

programed into the BDLC Analog Round Trip Delay Register register is the appropriate value for the transceiver being used. If these

conditions are not met, the symbol timings being measured on the SAE J1850 bus will be significantly affected. For a detailed description of

how symbol timings are measured on the SAE J1850 bus, refer to the appropriate SAE documents.

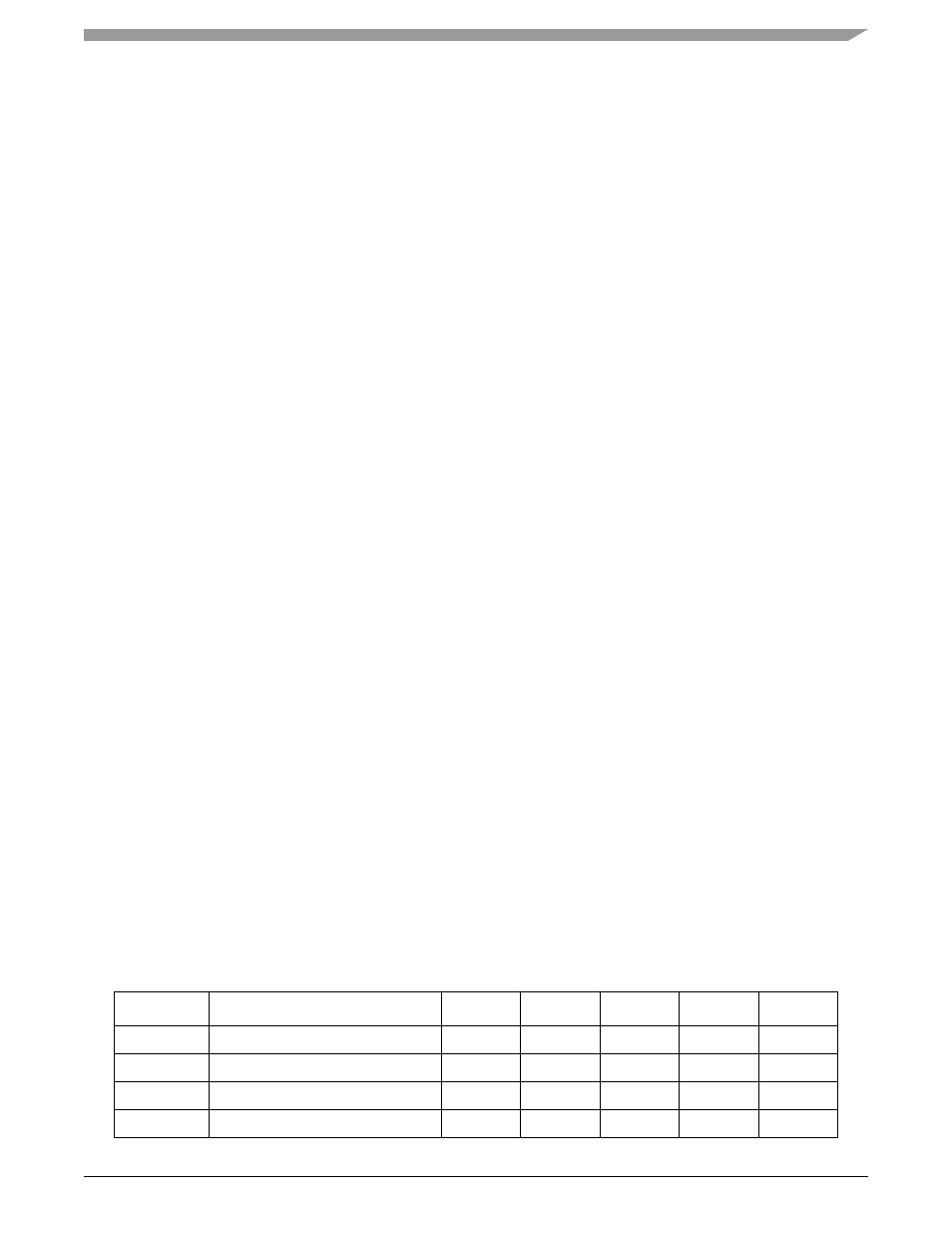

Table 20-13. BDLC Transmitter VPW Symbol Timing for Integer Frequencies

Number

Characteristic

Symbol

Min

Typ

Max

Unit

1

Passive Logic 0

T

tvp1

62

64

66

t

bdlc

2

Passive Logic 1

T

tvp2

126

128

130

t

bdlc

3

Active Logic 0

T

tva1

126

128

130

t

bdlc

4

Active Logic 1

T

tva2

62

64

66

t

bdlc