3 configuration sequence example for sir mode, 2 psc in mir mode, 1 block diagram and signal definition for mir mode – Freescale Semiconductor MPC5200B User Manual

Page 578: Configuration sequence example for sir mode -59, Psc in mir mode -60, Configuration sequence example for sir mode -60, Section 15.3.4.2, psc in mir, Mode

PSC Operation Modes

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-67

15.3.4.1.3

Configuration Sequence Example for SIR Mode

shows the configuration sequences. This list includes the SIR mode related registers only, not the other configure values like

interrupt and FIFO configurations. PSC module registers can be accessed by word or byte operations.

15.3.4.2

PSC in MIR Mode

The MIR mode is the second IrDA mode, which the PSC supports. This section will give some more informations about this mode. The

important register to configure the PSC6 (only this PSC supports the IrDA modes) for MIR mode are:

•

register - select the MIR mode

•

register - Channel Mode

•

If clock generate from the internal source:

— cdm_irda_bitclk_config - select Mclk frequency, see

Section 5.5.14, PSC6 (IrDA) Mclock Config Register—MBAR + 0x0234

— cdm_clock_enable_register - enable Mclk, see

Section 5.5.6, CDM Clock Enable Register—MBAR + 0x0214

—

- select BitClk and Frame Frequency

•

register - select full duplex and SIP mode

•

IRMDR register - select the clock divider

•

TFALARM

- select the FIFO “Alarm” level

•

register - enable or disable receiver and transmitter

•

Port_config - select the right Pin-Muxing, see

Chapter 2, Signal Descriptions

15.3.4.2.1

Block Diagram and Signal Definition for MIR Mode

The signal definitions for MIR mode are the same as in SIR mode. Please see

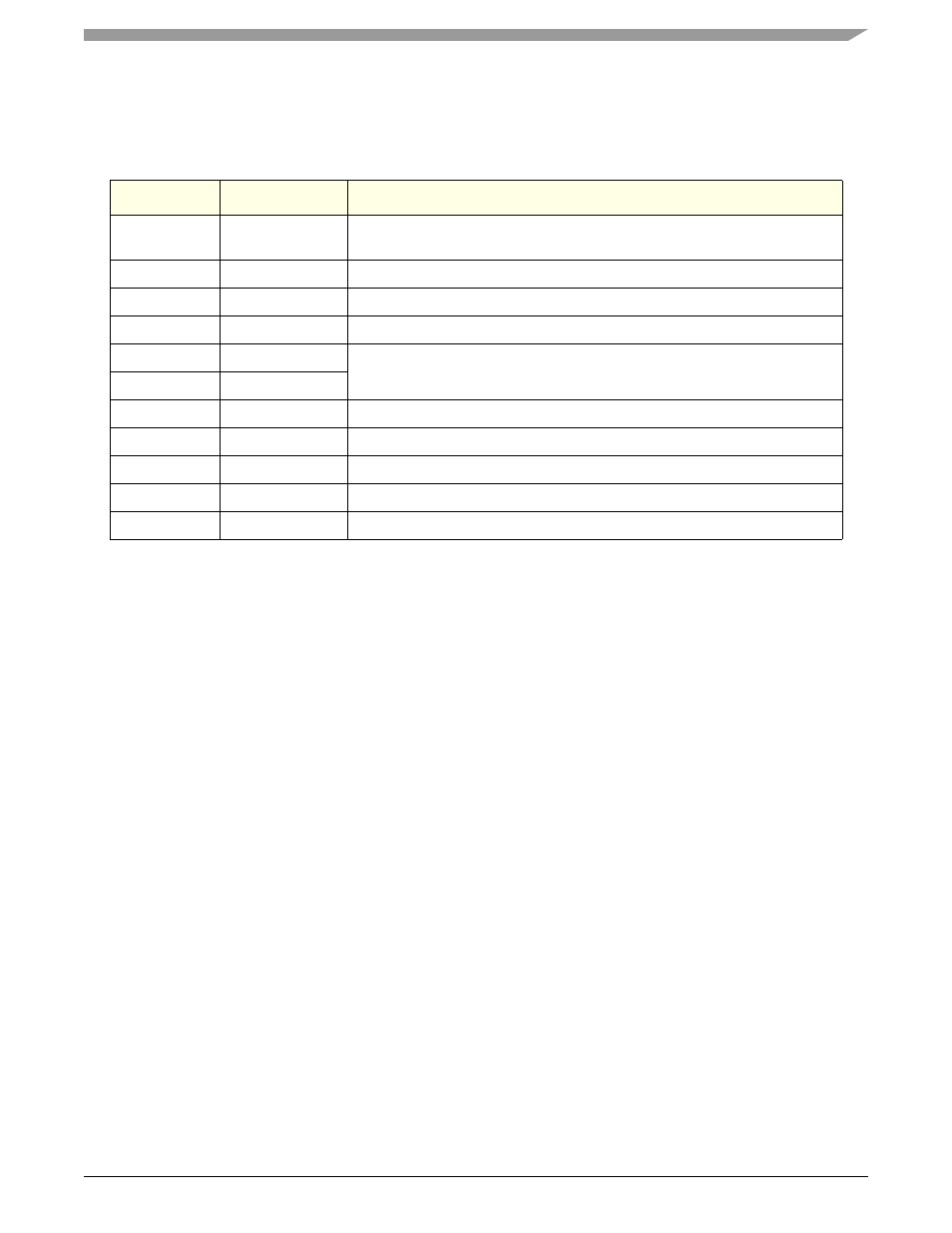

Table 15-91. Configuration Sequence Example for SIR Mode

Register

Value

Setting

0x0A

Disable the Tx and Rx part for configuration if the PSC was enabled by the work

before.

0x04000000

select the SIR mode

0x01

set SIR pulse width to 1.6 ms

0x6A

set counter for SIR pulse width for IPB clock 66 MHz

0x00

set the Baud rate to 9600 with IPB clock frequency 66 MHz

0xD7

0x0XXX

Choose Rx FIFO “almost full” threshold level.

TFALARM

0x0XXX

Choose Tx FIFO “almost empty” threshold level.

0xXXXX

select the desired interrupt

Port_Config

0x00500000

Select the Pin-Muxing for IrDA mode, see

Section 15.3.4.1, PSC in SIR Mode

0x05

Enable Tx and Rx