Freescale Semiconductor MPC5200B User Manual

Page 231

MPC5200B Users Guide, Rev. 1

7-72

Freescale Semiconductor

Real-Time Clock

7.6.3.8

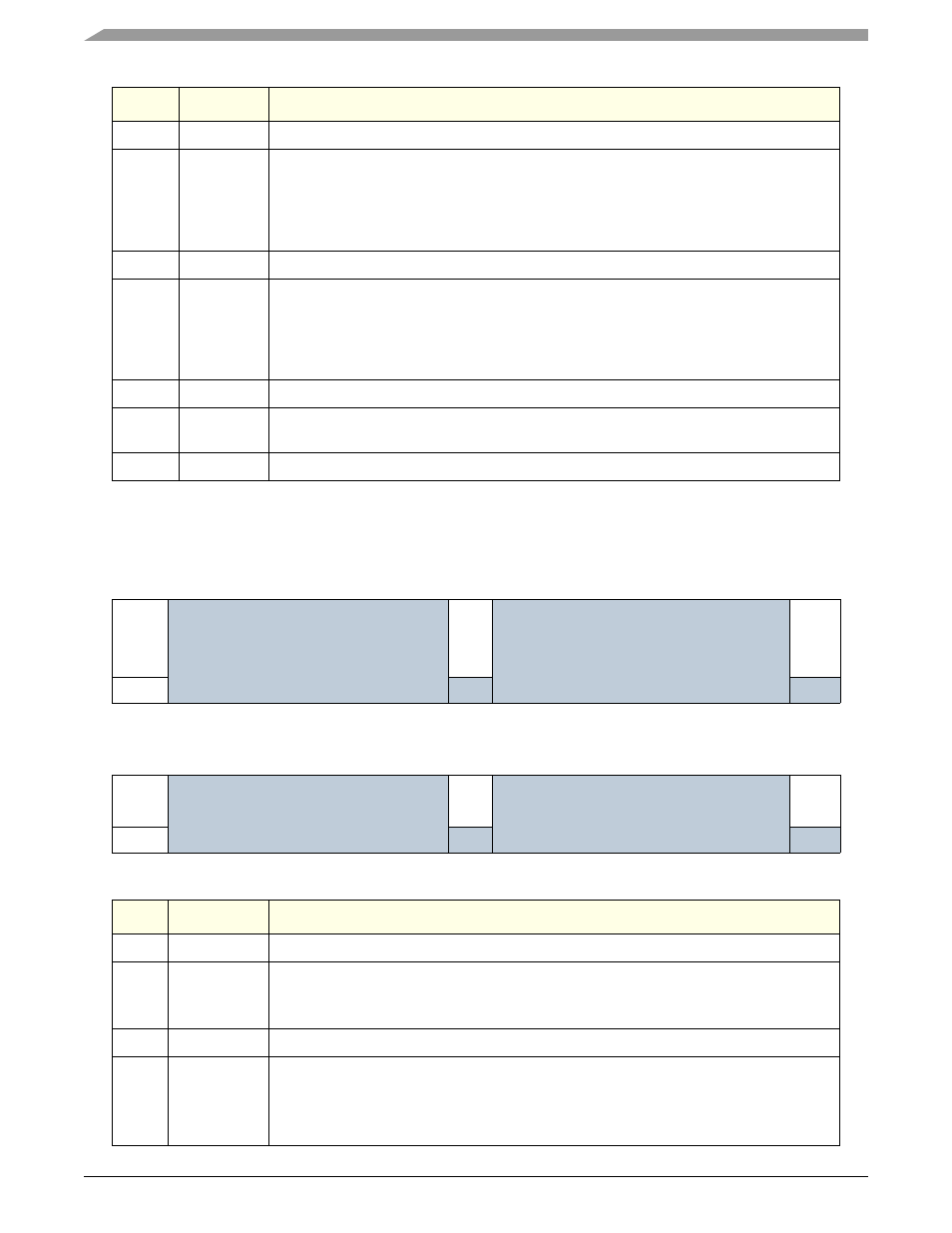

RTC Periodic Interrupt and Bus Error Register—MBAR + 0x081C

This is a read-only register.

Bits

Name

Description

0:6

—

Reserved

7

Int_alm

Status bit indicating that enabled once-a-day Alarm has occurred (active high). Alarm

interrupt has been activated. This bit and the Interrupt is cleared by writing 1 to this bit

position.

Note: A Stopwatch interrupt, if also active, must be cleared before the interrupt signal to the

CPU is negated.

8:14

—

Reserved

15

Int_SW

Status bit indicating that Stopwatch expiration has occurred (active high). Stopwatch

interrupt has been activated. This bit and the Interrupt are cleared by writing 1 to this bit

position.

Note: An Alarm interrupt, if also active, must be cleared before the interrupt signal to the

CPU is negated.

16:22

—

Reserved

23

Alm_status

Status bit indicating that once-a-day Alarm has occurred. Same as Int_alm bit above except

that clearing this bit does NOT clear the interrupt.

24:31

SW_min

Minutes remaining in stopwatch.

Table 7-63. RTC Periodic Interrupt and Bus Error Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

Bus_error_1

Reserved

Int_da

y

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

In

t_min

Reserved

Int_sec

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:6

—

Reserved

7

Bus_error_1

Internal status register—If high, indicates software has attempted a write access to a

read-only register in this module. No actual register contents are corrupted if this happens.

Cleared by writing 1 to this bit position.

8:14

—

Reserved

15

Int_day

Periodic interrupt at midnight. High indicates interrupt has occurred.

OR’d function of Int_day, Int_min and Int_sec produces RTC periodic interrupt to CPU

interface.

Cleared by writing 1 to this bit position.