Freescale Semiconductor MPC5200B User Manual

Page 478

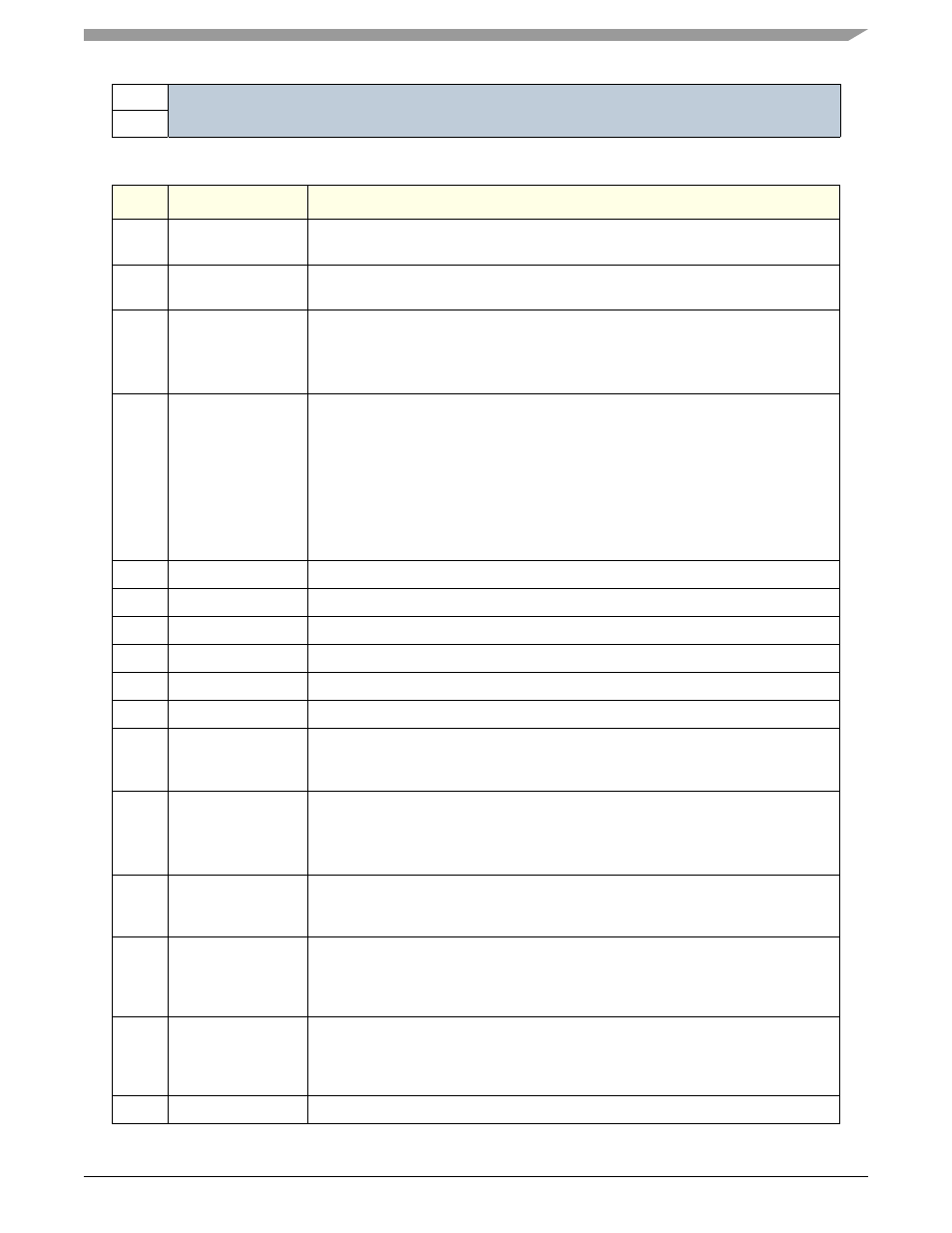

FEC Registers—MBAR + 0x3000

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

14-13

R

Reserved

W

Bits

Name

Description

0

HBERR

Heartbeat Error— interrupt bit indicates HBC is set in the X_CNTRL register and COL

input was not asserted within the heartbeat window following a transmission.

1

BABR

Babbling Receive Error—bit indicates frame was received with a length in excess of

R_CNTRL.MAX_FL bytes.

2

BABT

Babbling Transmit Error—bit indicates transmitted frame length exceeded

R_CNTRL.MAX_FL bytes. This condition is usually caused by a frame that is too long

being placed into the transmit data buffer(s).

Truncation does not occur.

3

GRA

Graceful Stop Complete—interrupt bit is asserted for one of three reasons.

1 = A graceful stop initiated by setting X_CNTRL.GTS bit is complete.

2 = A graceful stop initiated by setting X_CNTRL.FC_PAUSE bit is complete.

3 = A graceful stop initiated by reception of a valid full duplex flow control “pause”

frame is complete. Refer to “Full-Duplex Flow Control” section of the Ethernet

Operation chapter.

A "graceful stop" means the transmitter is put into a pause state after completion of

the frame currently being transmitted.

4

TFINT

Transmit frame interrupt. This bit indicates that a frame has been transmitted.

5

—

Reserved

6

—

Reserved

7

—

Reserved

8

MII

MII Interrupt—bit indicates MII completed the data transfer requested.

9

—

Reserved

10

LATE_COL

Late Collision bit indicates a collision occurred beyond the collision window (slot time)

in half-duplex mode. The frame is truncated with a bad CRC. Remainder of the frame

is discarded.

11

COL_RETRY_LIM

Collision Retry Limit—bit indicates a collision occurred on each of 16 successive

attempts to transmit the frame. The frame is discarded without being transmitted and

transmission of the next frame begins.

Only occurs in half-duplex mode.

12

XFIFO_UN

Transmit FIFO Underrun—bit indicates the transmit FIFO became empty before the

complete frame was transmitted. A bad CRC is appended to the frame fragment and

remainder of frame is discarded.

13

XFIFO_ERROR

Transmit FIFO Error—indicates an error occurred within the transmit FIFO. When

XFIFO_ERROR bit is set, ECNTRL.ETHER_EN is cleared, halting FEC frame

processing. When this occurs, software must ensure both the FIFO Controller and

BestComm are soft-reset.

14

RFIFO_ERROR

Receive FIFO Error—indicates error occurred within the RX FIFO. When

RFIFO_ERROR bit is set, ECNTRL.ETHER_EN is cleared, halting FEC frame

processing. When this occurs, software must ensure both the FIFO Controller and

BestComm are soft-reset.

15:31

—

Reserved.

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0