Freescale Semiconductor MPC5200B User Manual

Page 595

MPC5200B Users Guide, Rev. 1

16-8

Freescale Semiconductor

XLB Arbiter Registers—MBAR + 0x1F00

16.2.6

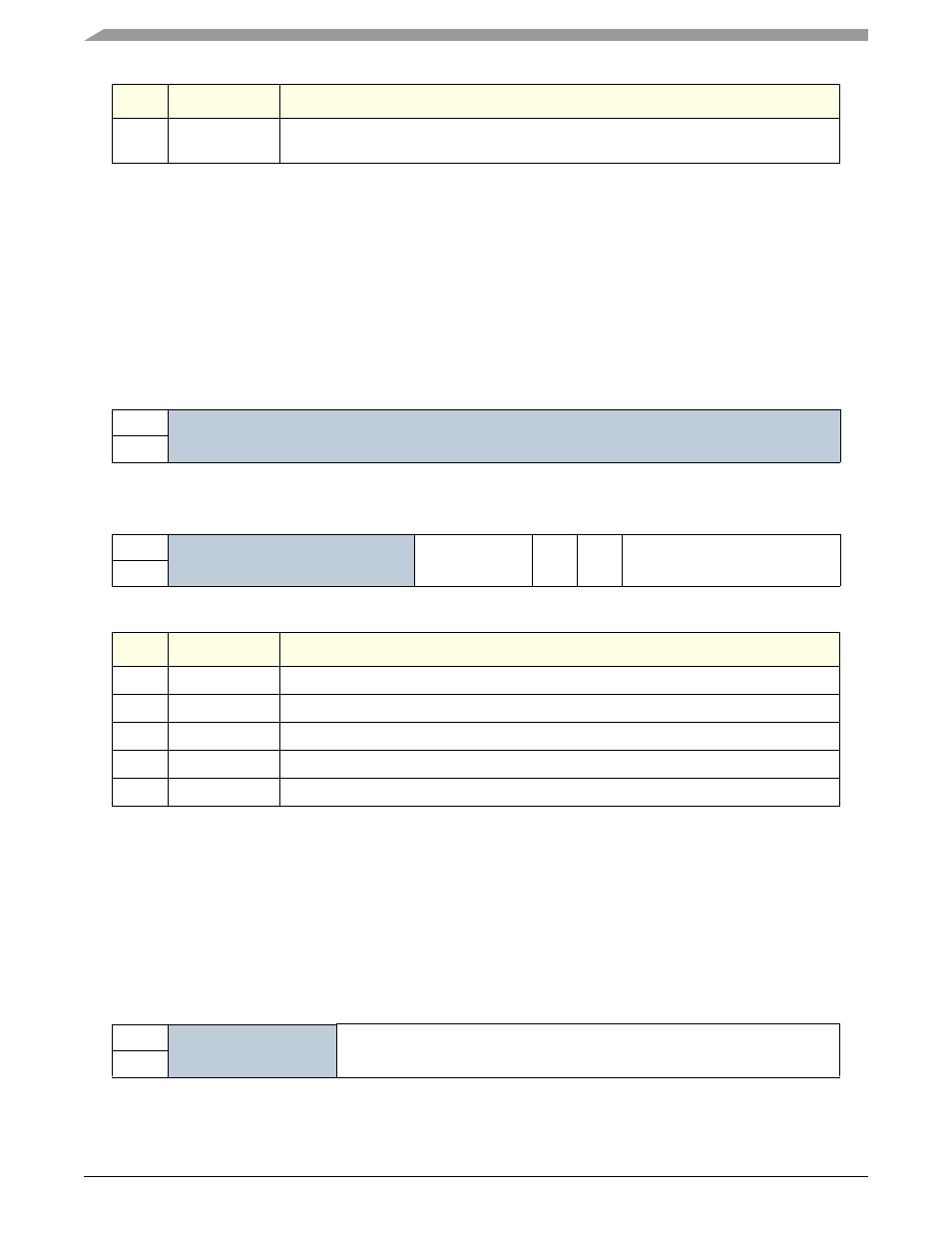

Arbiter Bus Signal Capture Register (R)—MBAR + 0x1F54

The Arbiter Bus Signal Capture Register captures TT, TBST, GBL, and TSIZ for an XLB address tenure that has either:

•

an address time-out,

•

a data time-out, or

•

a TEA from another source

These values are held until unlocked by writing any value to the Arbiter Address Capture Register or Arbiter Bus Signal Capture Register.

These values are also unlocked by writing 1 to either the Arbiter Status Register, bit 30 (Data Tenure Time-out Status) or bit 31 (Address

Tenure Time-Out Status). Unlocking the register does not clear its contents.

16.2.7

Arbiter Address Tenure Time-Out Register (R/W)—MBAR + 0x1F58

The Arbiter Address Tenure Time-out Register provides an expiration value to the arbiter watchdog for address tenures. After an address

tenure is initiated with a TS signal assertion by the master, the address tenure watchdog starts counting until either AACK is asserted, or the

counter expires. If expiration occurs before the AACK is encountered, the arbiter issues an AACK assertion, followed by a TEA assertion for

the corresponding data tenure. Subsequently, the Arbiter Status Register, bit 31 (AT) is set, and an interrupt is generated if the Arbiter Interrupt

Enable Register, bit 31 (ATE) is set.

The Arbiter Address Tenure watchdog can be enabled/disabled via the Arbiter Configuration Register, bit 30 (AT).

Bit

Name

Description

0:31

ADRCAP

Address Capture Value. This is the address that is captured when a bus error occurs. This

happens after an address time-out, data time-out, or any TEA assertion.

Table 16-6. Arbiter Bus Signal Capture Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Rsvd

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Rsvd

TSIZ[0:2]

GBL

TBST

TT[0:4]

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

0:21

—

Reserved

22:24

TSIZ

Captured Value of TSIZ[0:2].

25

GBL

Captured Value of GBL.

26

TBST

Captured Value of TBST.

27:31

TT

Captured Value of TT[0:4].

Table 16-7. Arbiter Address Tenure Time-Out Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Rsvd

ADRTO[4:15]

W

RESET:

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1