Freescale Semiconductor MPC5200B User Manual

Page 285

MPC5200B Users Guide, Rev. 1

9-20

Freescale Semiconductor

Programmer’s Model

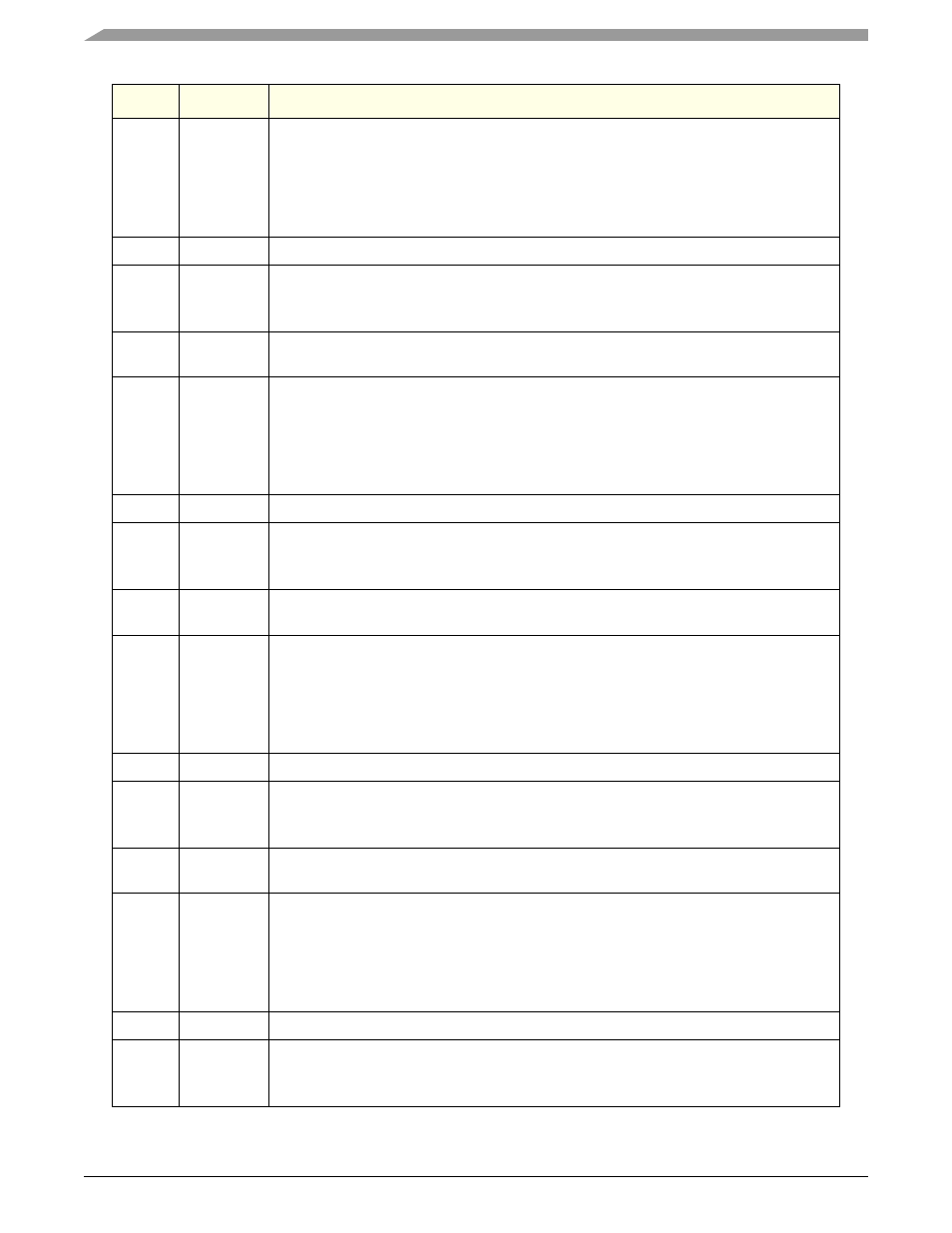

13

SLB4

Chip Select 4 Short/Long Burst, 0 for Short Burst only, 1 for Long Burst capable. Short burst

is 8-bytes, used for Instruction fetches, and CDWF cache line bursts on XLB if cache wrap

not capable. Long Burst capable means that peripheral can do 32-byte burst which hardware

will generate for cache line aligned XLB bursts (and CDWF if peripheral tagged as cache

wrap capable also).

This bit setting only applies in Large Flash or MOST Graphics Mode.

14

—

Reserved

15

BRE4

Chip Select 4 Burst Read Enable, 1 to enable peripheral bursting for given chip select. Must

be set to enable any Bursting reads.

This bit setting only applies in Large Flash or MOST Graphics Mode.

16

CW3

Chip Select 3 Cache Wrap capable, set if peripheral burst can perform PPC cache wrap. This

bit setting only applies in Large Flash or MOST Graphics Mode.

17

SLB3

Chip Select 3 Short/Long Burst, 0 for Short Burst only, 1 for Long Burst capable. Short burst

is 8-bytes, used for Instruction fetches, and CDWF cache line bursts on XLB if cache wrap

not capable. Long Burst capable means that peripheral can do 32-byte burst which hardware

will generate for cache line aligned XLB bursts (and CDWF if peripheral tagged as cache

wrap capable also).

This bit setting only applies in Large Flash or MOST Graphics Mode.

18

—

Reserved

19

BRE3

Chip Select 3 Burst Read Enable, 1 to enable peripheral bursting for given chip select. Must

be set to enable any Bursting reads.

This bit setting only applies in Large Flash or MOST Graphics Mode.

20

CW2

Chip Select 2 Cache Wrap capable, set if peripheral burst can perform PPC cache wrap. This

bit setting only applies in Large Flash or MOST Graphics Mode.

21

SLB2

Chip Select 2 Short/Long Burst, 0 for Short Burst only, 1 for Long Burst capable. Short burst

is 8-bytes, used for Instruction fetches, and CDWF cache line bursts on XLB if cache wrap

not capable. Long Burst capable means that peripheral can do 32-byte burst which hardware

will generate for cache line aligned XLB bursts (and CDWF if peripheral tagged as cache

wrap capable also).

This bit setting only applies in Large Flash or MOST Graphics Mode.

22

—

Reserved

23

BRE2

Chip Select 2 Burst Read Enable, 1 to enable peripheral bursting for given chip select. Must

be set to enable any Bursting reads.

This bit setting only applies in Large Flash or MOST Graphics Mode.

24

CW1

Chip Select 1 Cache Wrap capable, set if peripheral burst can perform PPC cache wrap. This

bit setting only applies in Large Flash or MOST Graphics Mode.

25

SLB1

Chip Select 1 Short/Long Burst, 0 for Short Burst only, 1 for Long Burst capable. Short burst

is 8-bytes, used for Instruction fetches, and CDWF cache line bursts on XLB if cache wrap

not capable. Long Burst capable means that peripheral can do 32-byte burst which hardware

will generate for cache line aligned XLB bursts (and CDWF if peripheral tagged as cache

wrap capable also).

This bit setting only applies in Large Flash or MOST Graphics Mode.

26

—

Reserved

27

BRE1

Chip Select 1 Burst Read Enable, 1 to enable peripheral bursting for given chip select. Must

be set to enable any Bursting reads.

This bit setting only applies in Large Flash or MOST Graphics Mode.

Bits

Name

Description