Command register (0x08) for all modes -11 – Freescale Semiconductor MPC5200B User Manual

Page 524

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-13

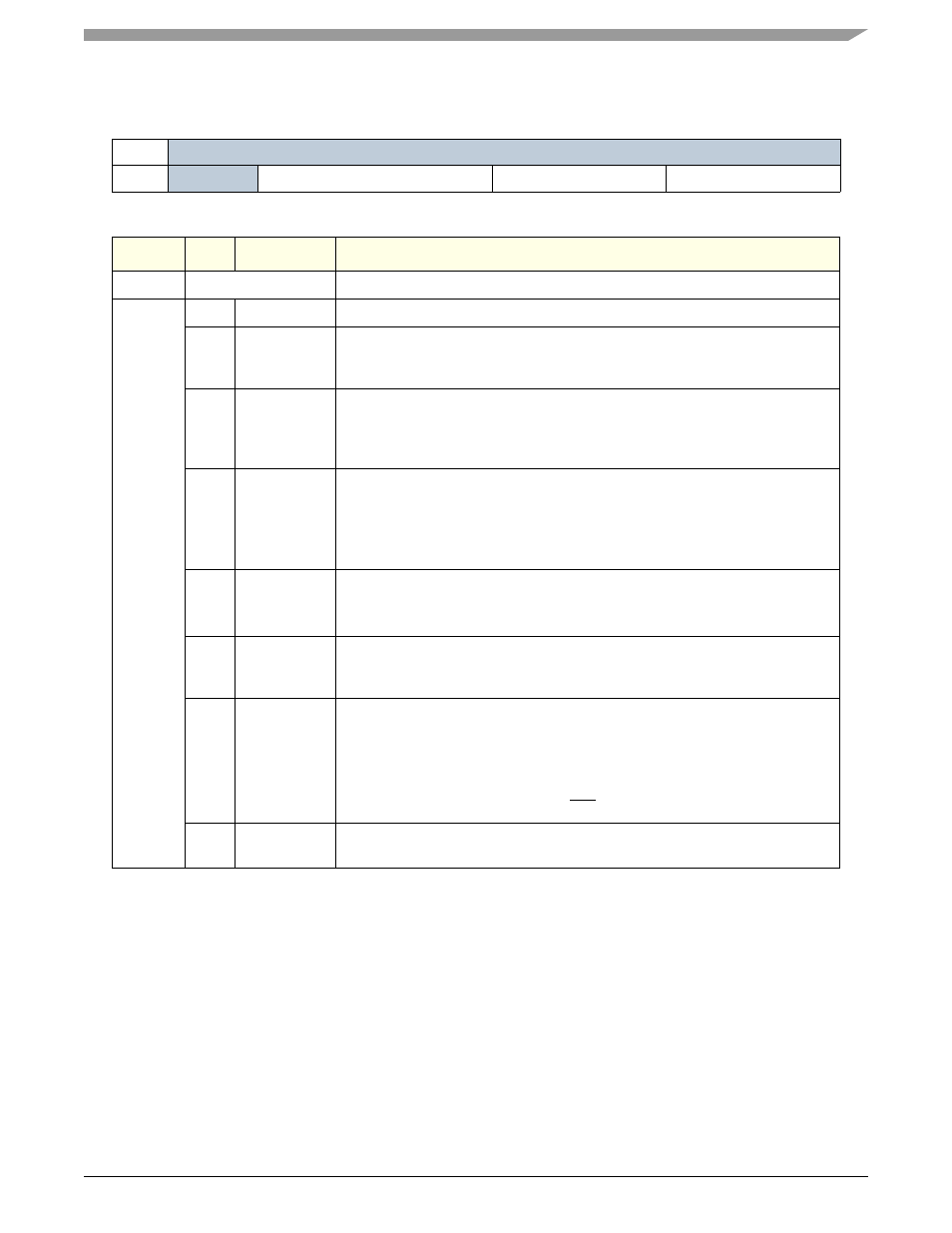

Table 15-16. Command Register (0x08) for all Modes

msb 0

1

2

3

4

5

6

7 lsb

R

Reserved

W

Reserved

MISC

TC

RC

RESET:

0

0

0

0

0

0

0

0

Bit

Value

Command

Description

0

—

Reserved

1:3

000

no command

—

001

reset mode

register

pointer

Causes MR register address to point to

010

reset

receiver

Immediately disables receiver, clears

[FFULL,RxRDY], and re-initializes

receiver FIFO pointer. No other registers are altered. Because it places the

receiver in a known state, use this command instead of RECEIVER DISABLE

when reconfigure the receiver.

011

reset

transmitter

In UART mode, immediately disables Tx and clears

[TxEMP,TxRDY]. No

other registers are altered. Because it places Tx in a known state, use this

command instead of TRANSMITTER DISABLE when reconfigure transmitter.

In Codec mode, URERR is not cleared by this soft reset. It is cleared the same

way as the Rx overflow bit, by a RESET ERROR STATUS command.

100

reset error

status

[RB,FE,PE,ORERR].

In Codec mode, command clears

[ORERR, URERR, DEOF, CMD_SEND,

DATA_OVR, DATA_VALID, UNEX_RX_SLOT]]

101

reset break

change

interrupt

Clears the delta break bit,

[DB]. Command has no effect in Codec mode.

110

start break

Forces TxD low

• If Tx is empty, break may be delayed up to one bit-time.

• If Tx is active, break starts when character transmission completes.

Break is delayed until any character in Tx shift register is sent. Any character in

Tx holding register is sent after the break. Tx must be enabled for command to be

accepted. This command ignores the

CTS state and has no effect in Codec mode.

111

stop break

Causes TxD to go high (mark) within two bit-times. Any characters in the Tx buffer

are sent.