Freescale Semiconductor MPC5200B User Manual

Page 50

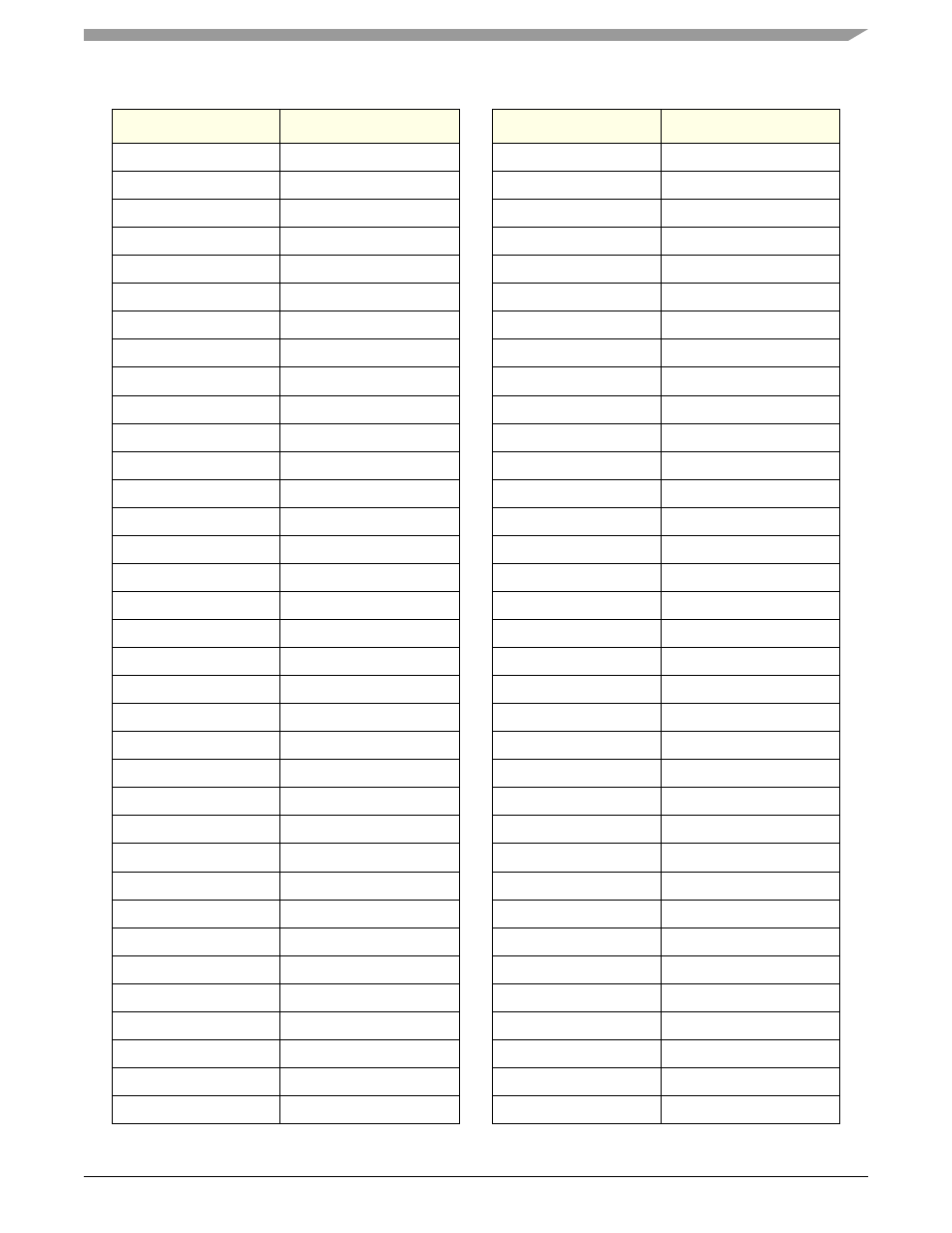

Pinout Tables

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

2-5

A11

PSC1_1

C06

PSC3_3

A12

PSC6_2

C07

PSC3_0

A13

PORRESET

C08

CORE_PLL_AVDD

A14

SRESET

C09

PSC2_0

A15

SYS_XTAL_IN

C10

PSC1_2

A16

MEM_MA_1

C11

PSC6_1

A17

MEM_MBA_1

C12

GPIO_WKUP_7

A18

MEM_RAS

C13

PSC6_3

A19

MEM_WE

C14

SYS_PLL_AVSS

A20

MEM_DQM_2

C15

GPIO_WKUP_6

B01

TEST_SEL_0

C16

MEM_MA_3

B02

TEST_MODE_0

C17

MEM_MA_0

B03

JTAG_TRST

C18

MEM_MBA_0

B04

JTAG_TCK

C19

MEM_MA_5

B05

PSC3_7

C20

MEM_MA_6

B06

PSC3_4

D01

TIMER_4

B07

PSC3_1

D02

TIMER_3

B08

PSC2_3

D03

TIMER_2

B09

PSC2_1

D04

VSS_IO/CORE

B10

PSC1_3

D05

VDD_CORE

B11

PSC1_0

D06

VDD_IO

B12

PSC6_0

D07

VDD_CORE

B13

HRESET

D08

LP_OE

B14

SYS_PLL_AVDD

D09

VDD_IO

B15

SYS_PLL_TPA

D10

VDD_CORE

D11

VDD_CORE

H04

VDD_IO

D12

VDD_MEM_IO

H17

VDD_MEM_IO

D13

VDD_MEM_IO

H18

MEM_MDQ_20

D14

SYS_XTAL_OUT

H19

MEM_DQM_1

D15

VDD_MEM_IO

H20

MEM_MDQS_1

D16

VSS_IO/CORE

J01

ETH_3

D17

VDD_MEM_IO

J02

ETH_4

D18

MEM_MDQS_2

J03

ETH_10

D19

MEM_MA_7

J04

ETH_17

D20

MEM_MA_8

J09

VSS_IO/CORE

Table 2-1. Signals by Ball/Pin (continued)

Ball/Pin

Pin Name

Ball/Pin

Pin Name