10 interrupt status register (0x14) - isr, Interrupt status register (0x14) — isr -18, Interrupt status register (0x14) other modes -18 – Freescale Semiconductor MPC5200B User Manual

Page 530: Interrupt status register (0x14) — isr

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-19

15.2.10

Interrupt Status Register (0x14)

—

ISR

The read-only ISR register provides status for all potential interrupt sources. Register contents is masked by the

.

•

If an ISR flag sets and the corresponding

bit is also set, the internal interrupt output is asserted.

•

If the corresponding

bit is cleared, the ISR bit state has no effect on the interrupt output.

6

IEC1

Interrupt enable control for D_DCD.

0 = D_DCD has no effect on the IPC in the

1 = When the D_DCD becomes high, IPC bit in the

sets (causing an interrupt if mask

is set).

7

IEC0

Interrupt enable control for D_CTS.

0 = D_CTS has no effect on the IPC in the

.

1 = When the D_CTS becomes high, IPC bit in the

sets (causing an interrupt if mask

is set).

After enable the PSC the D_CTS bit can be set, therefore it’s important to clear the D_CTS bit

before enable this interrupt.

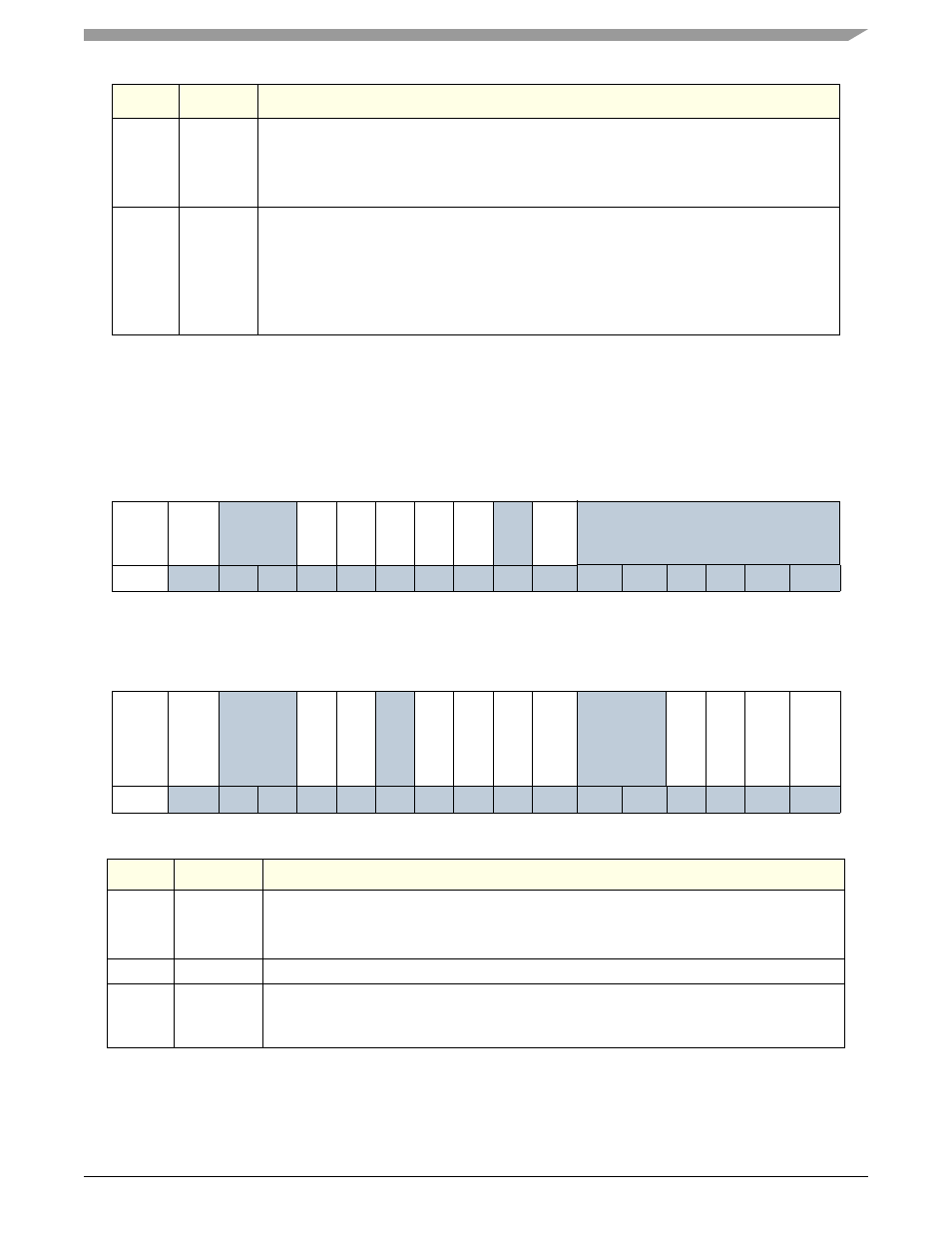

Table 15-26. Interrupt Status Register (0x14) for UART / SIR Mode

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 lsb

R

IPC

Reserved

ORERR

Tx

EMP

DB

RxR

D

Y

FF

U

L

L

Tx

RD

Y

Re

ser

v

ed

Error

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Table 15-27. Interrupt Status Register (0x14) other Modes

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 lsb

R

IPC

Reserved

ORERR

URERR

Reser

v

ed

RxR

D

Y

FF

ULL

Tx

RD

Y

DEOF

Error

Reserved

CM

D_SEND

DATA_

O

VR

DATA_

V

AL

ID

UN

EX_

R

X_

SLOT

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

0

IPC

Input port change interrupt.

0 = No IPC event was occurred.

1 = An IPC event was occurred.

1 :2

—

Reserved

3

ORERR

Overrun Error

This bit is identical to the ORERR bit in the

register. To clear this interrupt use the reset

error status command in the

register.

Bit

Name

Description