1 machine check pin-core_mcp, 2 system management interrupt-core_smi, 3 standard interrupt-core_int – Freescale Semiconductor MPC5200B User Manual

Page 161

MPC5200B Users Guide, Rev. 1

7-2

Freescale Semiconductor

Interrupt Controller

does not include machine-check bus errors or transaction handshaking. e300 core interrupt pins given in

through

Section 7.2.1.3, Standard Interrupt—core_int

show e300 core interrupt priority.

7.2.1.1

Machine Check Pin—core_mcp

NOTE

The core_mcp pin is not used. Bus errors occur on the XL bus, thus generating an internal

machine-check exception, or are reflected as a normal interrupt from the offending source module.

Internally, bus errors (TEA, APE, DPE, etc.) cause a machine check exception to a single exception vector. This pin allows additional, external

to the e300 core, interrupts of the same type, but is not connected in this device.

7.2.1.2

System Management Interrupt—core_smi

The core_smi is a e300 core pin for high priority interrupts.

defines the interrupts.

7.2.1.3

Standard Interrupt—core_int

Identical to core_smi, but of lower priority. This interrupt is shared by a variety of internal low priority interrupts such as GPIO and RTC

functions. Some programmable connection are provided.

gives a summary of the interrupt pins.

shows the interrupt

sources and e300 core pins.

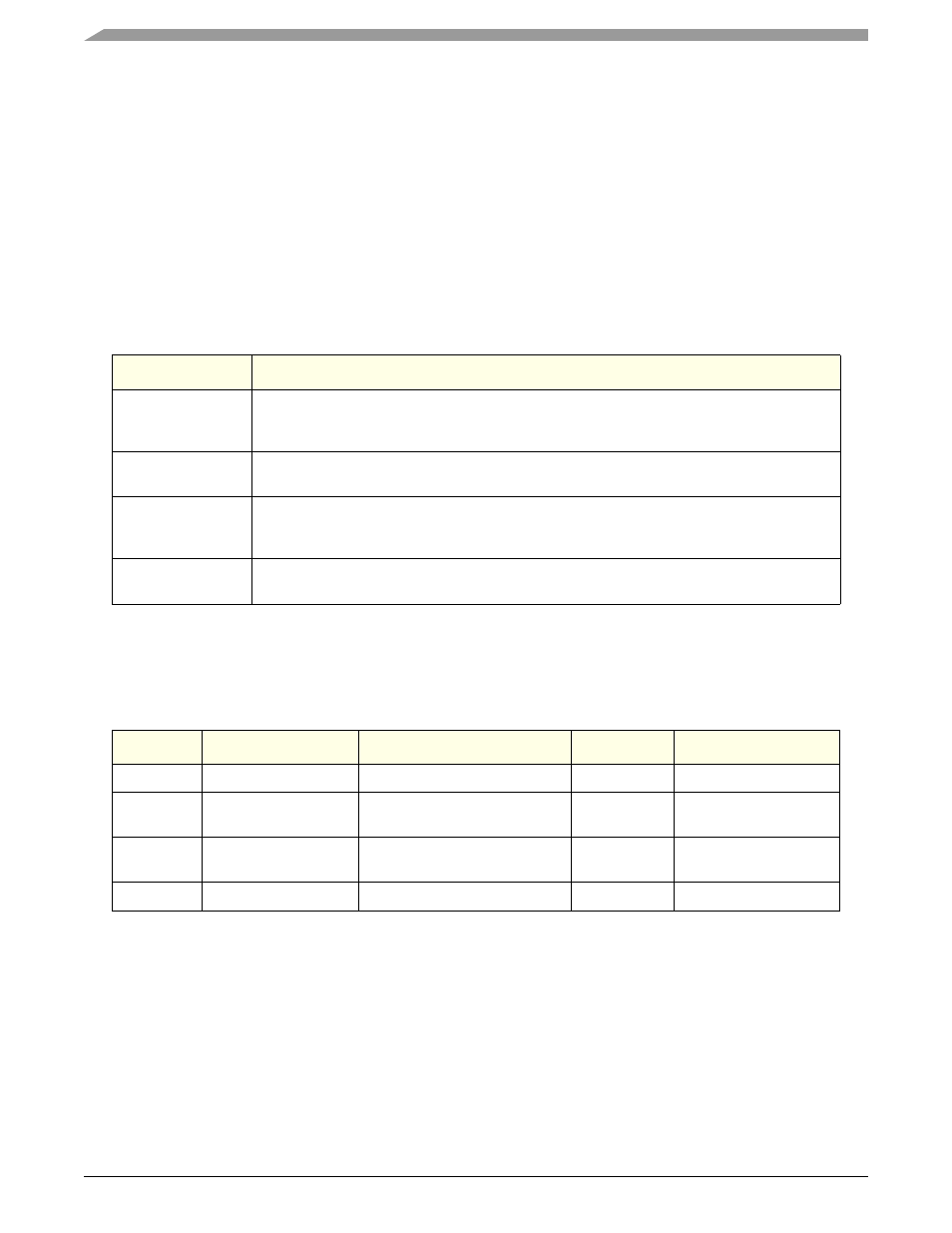

Table 7-2. System Management Interrupt Pin Interrupts

Interrupt

Description

Enables

The MSR[ee] bit must be set to enable interrupts at this e300 core pin. The MSR[ee] bit is

automatically cleared when an interrupt occurs. Therefore, the exception handler must re-set

this bit when interrupt is cleared.

Recovery/Status

Recovery is highly dependant on system and software design. Where multiple sources are tied

to the same interrupt, a status register is provided to distinguish the interrupting source.

Timing

Assertion of this interrupt is persistent (i.e., interrupt remains until cleared). If other interrupts

are pending when first interrupt is cleared, the core_smi pin should remain asserted for

handling once the current exception handler re-sets the MSR[ee] bit.

Connections

Standard external and internal interrupts can be connected to this high priority interrupt. Slice

timer 1 is a dedicated connection.

Table 7-3. e300 core Interrupt Pins Summary

Pin

Description

Sources

To Enable

Timing

core_mcp

Machine Check Pin

Tied inactive

—

—

core_cint

Critical Interrupt

BestComm HI, IRQ0,

Slice Timer 0, CCS WakeUp

MSR[ce]

Persistent

(remains until cleared)

core_smi

System Management

Interrupt

Slice Timer 1,

Programmable interrupts

MSR[ee]

Persistent

core_int

Standard Interrupt

Programmable interrupts

MSR[ee]

Persistent