3 configuration sequence example for fir mode, 4 psc fifo system, Configuration sequence example for fir mode -64 – Freescale Semiconductor MPC5200B User Manual

Page 582: Section 15.4, psc fifo system

PSC FIFO System

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-71

NOTE

The FIR module doesn’t support the CRC generation. If the transfer require a CRC Field use the CRC

generation from the BestComm module. See also

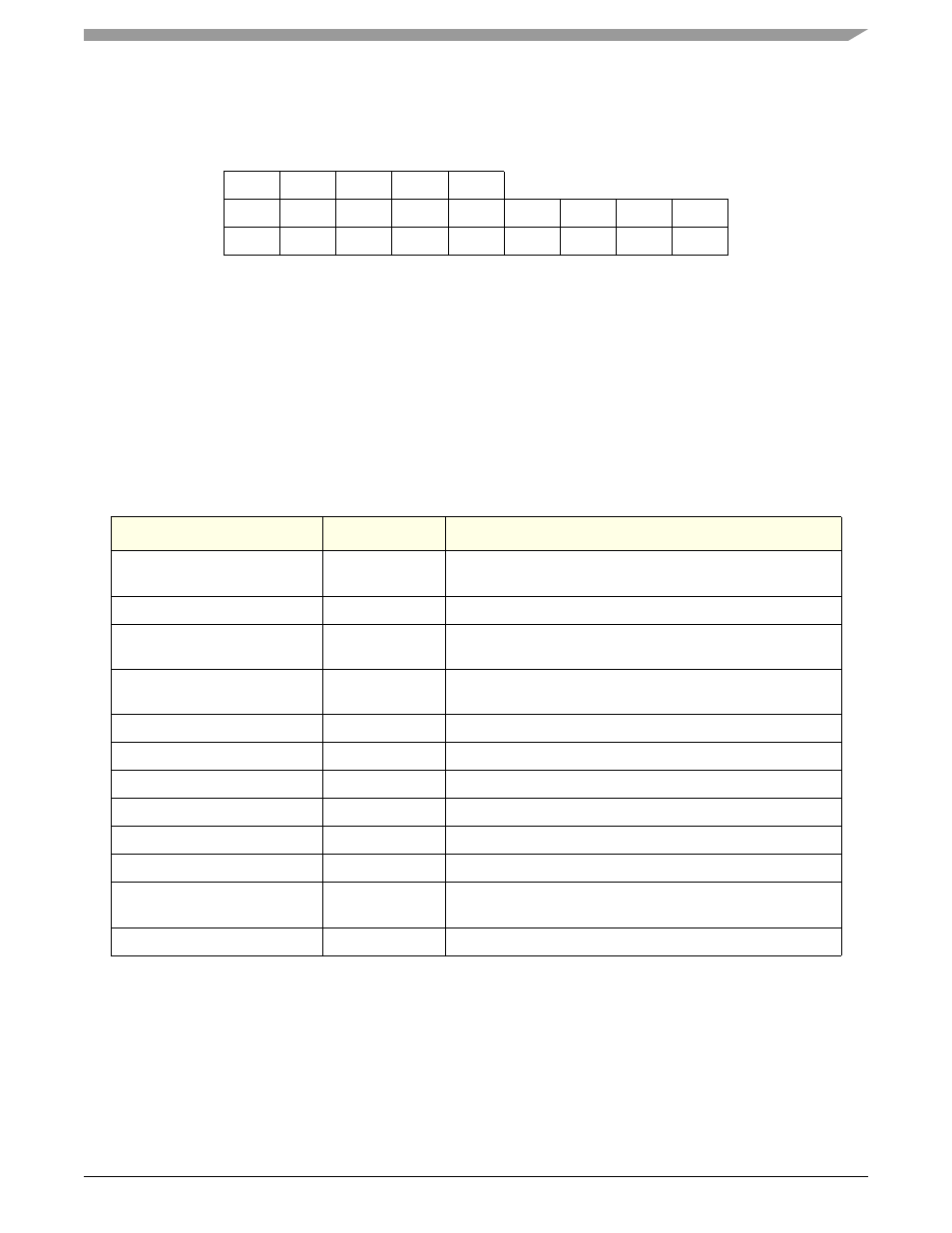

The chip patterns for PA, STA and STO are defined as:

The FIR system must emit SIP (Serial Interaction Pulse), for more informations see

Section 15.3.4.2.3, Serial Interaction Pulse (SIP).

NOTE

Please choose first the desired mode (FIR mode) than configure the port (write to port_config

register). This sequence will avoid pulses on the TX line during port configuration. This is very

important for all IrDA (SIR, MIR, and FIR) modes.

15.3.4.3.3

Configuration Sequence Example for FIR Mode

The

Table 15-93

shows the configuration sequences. This list includes the FIR mode related registers only, not the other configure values like

interrupt and FIFO configurations. PSC module registers can be accessed by word or byte operations.

15.4

PSC FIFO System

The receive FIFO stack consists of the FIFO and a receiver shift register connected to the RxD. Data is assembled in the receiver shift register

and loaded into the FIFO at the location pointed to by the FIFO Write Pointer.

Reading the Rx buffer produces an output of data from the location pointed to by the FIFO Read Pointer. After the read cycle data at the top

of the FIFO stack is popped and the Rx shift register can add new data at the bottom of the FIFO. The standard FIFO Controller used in

MPC5200 peripherals, such as the PSCs, was designed to control either:

•

a transmit (Tx) FIFO

•

a receive (Rx) FIFO

PA

1000

0000

1010

1000

(16 times repeated)

STA

0000

1100

0000

1100

0110

0000

0110

0000

STO

0000

1100

0000

1100

0000

0110

0000

0110

first chip

last chip

Table 15-93. Configuration Sequence Example for FIR Mode

Register

Value

Setting

0x0A

Disable the Tx and Rx part for configuration if the PSC was

enabled by the work before.

0x06800000

Select the FIR mode, use internal clock

cdm_irda_bitclk_config

0x8002

set Mclk to 176 Mhz, see

Section 5.5.14, PSC6 (IrDA) Mclock

cdm_clock_enable_register

0x00000010

Section 5.5.6, CDM Clock Enable

0x0001

set IrdaClk to 88 MHz

0x02

enable SIP

0x0A

set bit clock frequency = 8 MHZ with Mclk frequency = 88 MHz

0x0XXX

Choose Rx FIFO “almost full” threshold level.

TFALARM

0x0XXX

Choose Tx FIFO “almost empty” threshold level.

0xXXXX

select the desired interrupt

Port_Config

0x00F00000

Select the Pin-Muxing for IrDA mode, see

0x05

Enable Tx and Rx