Freescale Semiconductor MPC5200B User Manual

Page 170

Interrupt Controller

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

7-11

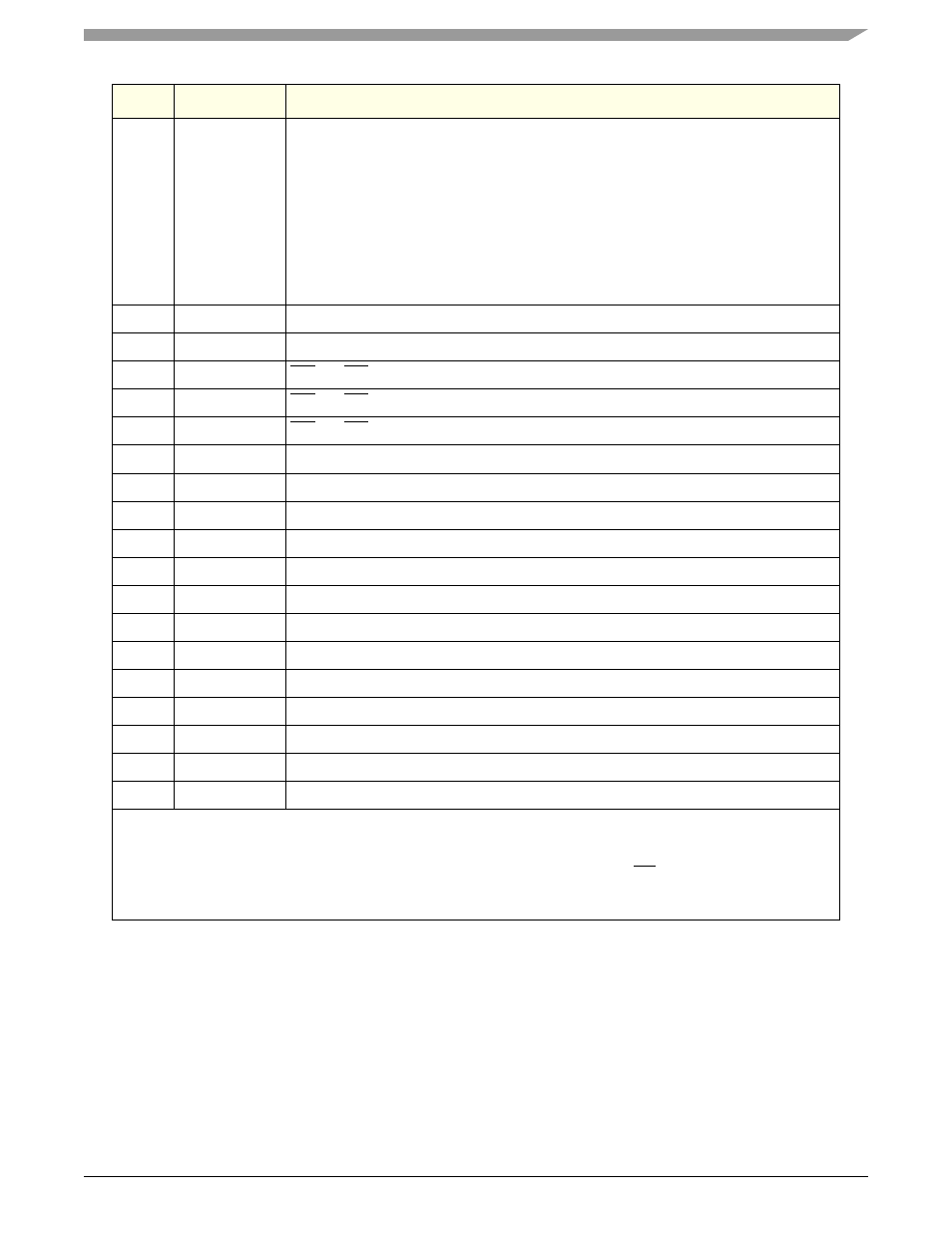

—

Main_Mask[x]

To mask/accept individual main interrupt sources (as opposed to peripheral or critical

interrupt sources). This masking is in addition to interrupt enables, which may exist in each

source module.

0=Default. Accept interrupt from source module.

1=Ignore interrupt from source module.

Take care if masking LO_int, which is a collection of multiple Peripheral sources in a single

presentation. Masking LO_int essentially prevents any LO Peripheral from generating an

interrupt, even when those interrupts are enabled (i.e., unmasked) in Per_Mask, Reg0.

Important

—See Note

1

.

15

Main_Mask0

Slice Timer 1, which is hardwired to SMI interrupt output. See Note

2

.

—

—

Interrupt sources below are bank/priority programmable (in Reg6 and Reg7).

16

Main_Mask1

IRQ[1] (IRQ[1] input pin interrupt)

17

Main_Mask2

IRQ[2] (IRQ[2] input pin interrupt)

18

Main_Mask3

IRQ[3] (IRQ[3] input pin interrupt)

19

Main_Mask4

LO_int (source programmable from Peripheral ints)

20

Main_Mask5

RTC_pint (Real time clock, periodic interrupt)

21

Main_Mask6

RTC_sint (Real time clock, stopwatch and alarm interrupt)

22

Main_Mask7

GPIO_std (collected GPIO interrupts, non-WakeUp)

23

Main_Mask8

GPIO_wkup (collected WakeUp interrupts)

24

Main_Mask9

TMR0 (internal Timer resource)

25

Main_Mask10

TMR1 (internal Timer resource)

26

Main_Mask11

TMR2 (internal Timer resource)

27

Main_Mask12

TMR3 (internal Timer resource)

28

Main_Mask13

TMR4 (internal Timer resource)

29

Main_Mask14

TMR5 (internal Timer resource)

30

Main_Mask15

TMR6 (internal Timer resource)

31

Main_Mask16

TMR7 (internal Timer resource)

Note:

1.

Setting these bits prevents an interrupt being presented to the masked sources e300 core pins. Encoded status

indications (MSe in Reg9) are therefore suppressed, but the binary all status bits (MSa in RegB) are active as long as

the source module is presenting an active input to the Interrupt Controller. Masking IRQ[1:3], is redundant with External

ENA bits in Reg4, but both masks are applied.

2.

Slice Timer 1 is hard-coded and neither bank nor priority adjustable.

Bits

Name

Description