27 infrared fir divide register (0x54)-irfdr, Infrared fir divide register (0x54)—irfdr -31, Frequency selection in mir mode -31 – Freescale Semiconductor MPC5200B User Manual

Page 547: Infrared fir divide register (0x54)—irfdr

MPC5200B Users Guide, Rev. 1

15-36

Freescale Semiconductor

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

15.2.27

Infrared FIR Divide Register (0x54)—IRFDR

This register set the FIR mode Baud rate. This register is reserved in other modes.

Bit

Name

Description

0

FREQ

MIR—0.576 M bps mode.

0 = The Baud rate is 1.152 M bps.

1 = If the Baud rate is 0.576 Mbps, this bit should be set high in order to output 1.

For more informations about the SIP pulse see also

other Modes—Reserved

1:7

M_FDIV

MIR—Clock divide ratio in MIR mode. The bit frequency is derived by:

This bit frequency should be 0.576 or 1.152 MHz. In order to send a quarter bit duration pulse

and receive minimum pulse described in the IrDA spec, (M_FDIV + 1) should be a factor of 4

and larger than or equal to 8.

shows the selectable divide factor and the input clock

frequency on IrdaClk port. For more informations about the frequency generation see also

Section 15.2.14, Codec Clock Register (0x20)—CCR

other Modes—Reserved

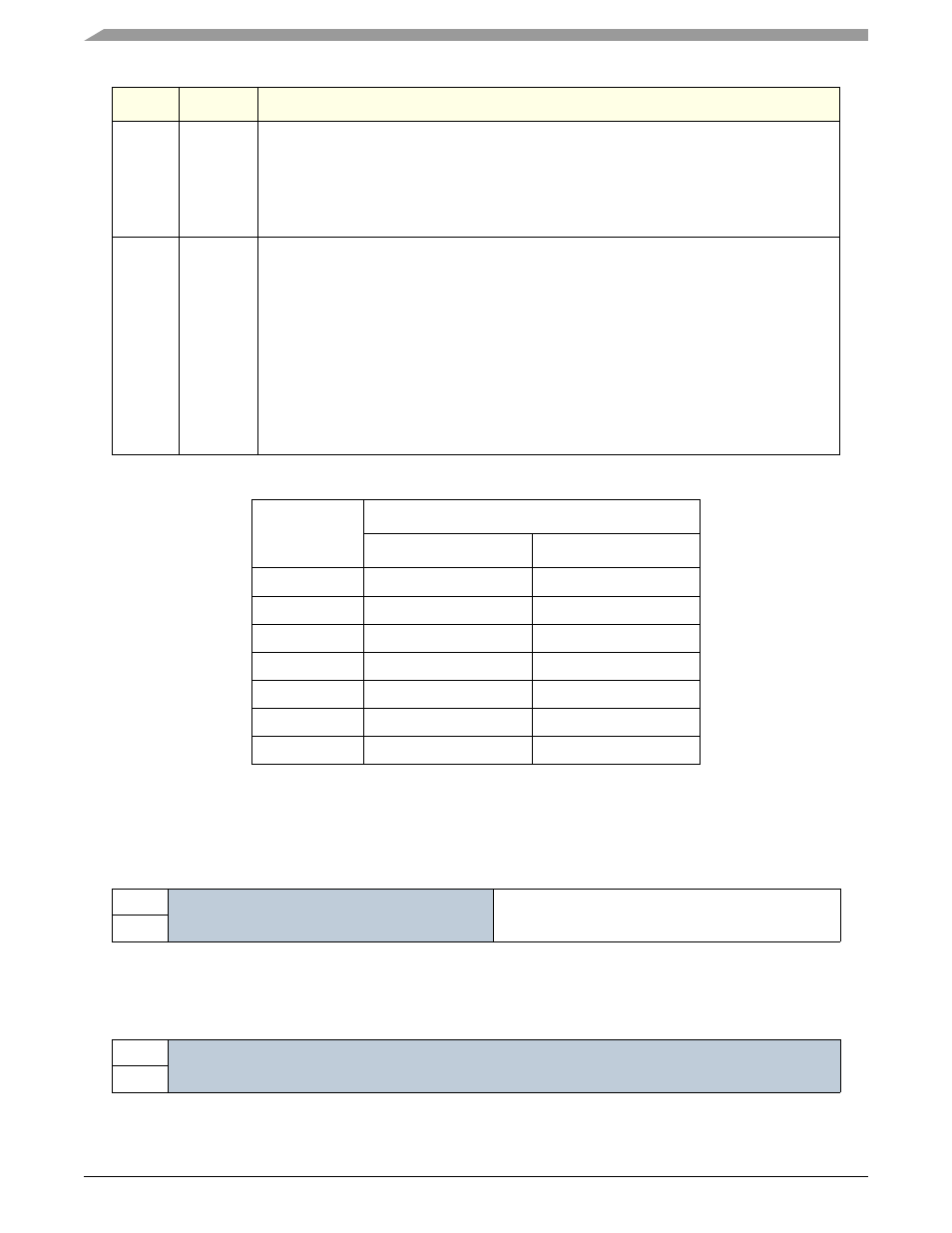

Table 15-53. Frequency Selection in MIR Mode

M_FDIV[1:7]

Frequency of IrdaClk [MHz]

1.152 Mbps

0.576 Mbps

0x07

9.216

4.6080

0x0B

13.824

6.912

0x0F

18.432

9.216

0x13

23.040

11.520

0x17

27.648

13.824

...

...

...

0x7F

147.456

73.728

Table 15-54. Infrared FIR Divide Register (0x54) for MIR Mode

msb 0

1

2

3

4

5

6

7 lsb

R

Reserved

F_FDIV

W

RESET:

0

0

0

0

0

0

0

0

Table 15-55. Infrared FIR Divide Register (0x54) for other Modes

msb 0

1

2

3

4

5

6

7 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

fbit

fIrdaClk

M_FDIV + 1

-------------------------------

=