Freescale Semiconductor MPC5200B User Manual

Page 427

MPC5200B Users Guide, Rev. 1

12-24

Freescale Semiconductor

Host Control (HC) Operational Registers

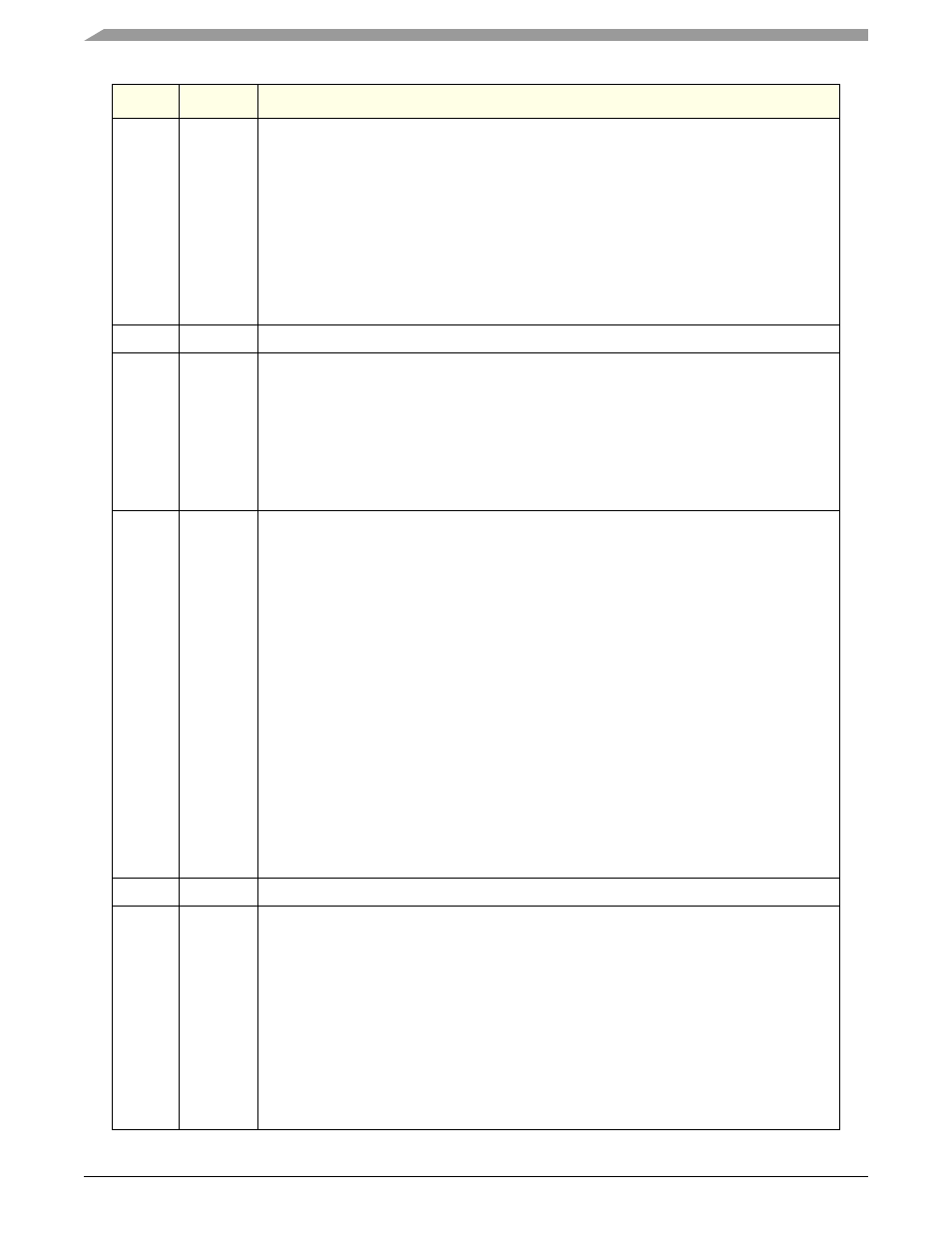

15

CSC

ConnectStatusChange—bit is set whenever a connect or disconnect event occurs.

•

Writing 1 causes HC to clear this bit.

•

Writing 0 has no effect.

If CCS is cleared when a SetPortReset, SetPortEnable, or SetPortSuspend write occurs, this

bit is set to force the driver to re-evaluate the connection status since these writes should not

occur if the port is disconnected.

0 = No change in CCS

1 = Change in CCS

If the DeviceRemovable[NDP] bit is set, this bit is set only after a Root Hub reset to notify the

system that the device is attached.

16:21

—

Reserved

22

LSDA

LowSpeedDeviceAttached (read)—bit indicates the speed of the device attached to this port.

0 = Full speed device attached

1 = Low speed device attached

This field is valid only when CurrentConnectStatus is set.

ClearPortPower (write)

•

Writing 1 causes HC to clear the PortPowerStatus bit.

•

Writing 0 has no effect.

23

PPS

PortPowerStatus (read)—bit reflects the port power status, regardless of the type of power

switching implemented.

If an overcurrent condition is detected, this bit is cleared. HCD sets this bit by writing

SetPortPower or SetGlobalPower. HCD clears this bit by writing ClearPortPower or

ClearGlobalPower. Which power control switches are enabled is determined by

PowerSwitchingMode and PortPortControlMask[NDP].

In global switching mode (PSM=0), only Set/ClearGlobalPower controls this bit.

In per-port power switching (PSM=1), if the PortPowerControlMask[NDP] bit for the port is

set, only Set/ClearPortPower commands are enabled.

If the mask is not set, only Set/ClearGlobalPower commands are enabled.

If port power is disabled, CurrentConnectStatus, PortEnableStatus, PortSuspendStatus, and

PortResetStatus should be reset.

0 = Port power is off

1 = Port power is on

SetPortPower (write)

•

Writing causes HC to set the PortPowerStatus bit.

•

Writing 0 has no effect.

If power switching is not supported, this bit always reads ‘1b’.

24:26

—

Reserved

27

PRS

PortResetStatus (read)—When this bit is set by a write to SetPortReset, port reset signaling

is asserted. When reset is completed, this bit is cleared when PortResetStatusChange is set.

This bit cannot be set if CurrentConnectStatus is cleared.

0 = Port reset signal is not active

1 = Port reset signal is active

SetPortReset (write)

•

Writing 1 causes HC to set port reset signaling.

•

Writing 0 has no effect.

If CurrentConnectStatus is cleared, a write does not set PortResetStatus. Instead, it sets

ConnectStatusChange. This notifies the driver that an attempt was made to reset a

disconnected port.

Bits

Name

Description