5 fec rx fifo read pointer register-mbar + 0x319c, Fec rx fifo alarm pointer register -32, Fec rx fifo read pointer register -32 – Freescale Semiconductor MPC5200B User Manual

Page 497: Section 14-35, fec rx fifo alarm pointer register, Section 14-36, fec rx fifo read pointer register

MPC5200B Users Guide, Rev. 1

14-32

Freescale Semiconductor

FEC Tx FIFO Status Register—MBAR + 0x31A8

14.8.5

FEC Rx FIFO Read Pointer Register—MBAR + 0x319C

FEC Tx FIFO Read Pointer Register—MBAR + 0x31BC

The RFIFO_RDPTR and TFIFO_RDPTR are a FIFO-maintained pointer which point to the next FIFO location to be read. The read pointer

can be both read and written.

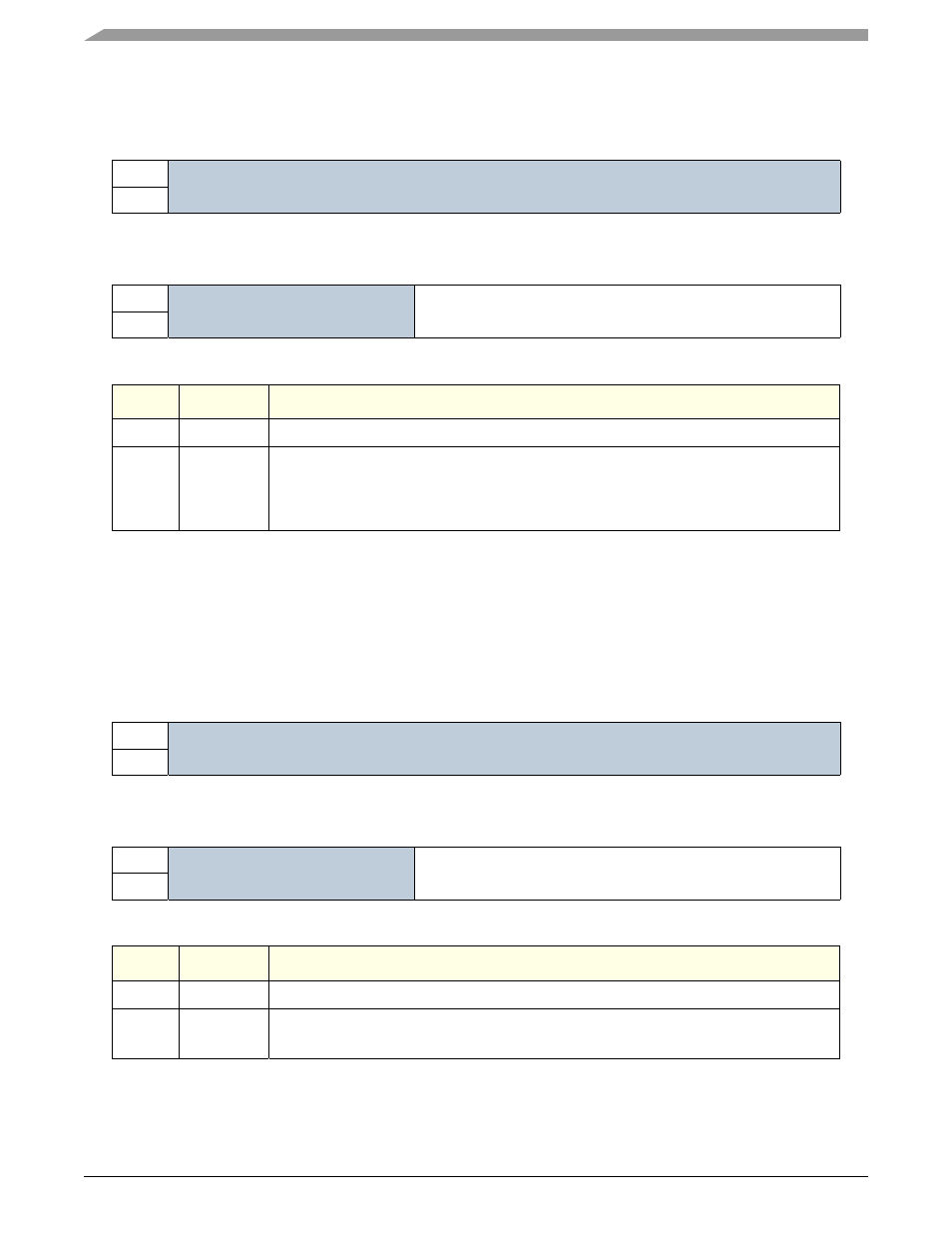

Table 14-35. FEC Rx FIFO Alarm Pointer Register

FEC Tx FIFO Alarm Pointer Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

Alarm[9:0]

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:21

—

Reserved

22:31

Alarm[9:0]

Alarm Pointer.

This pointer indicates the point at (or below) which to assert the FIFO alarm signal. This

value is compared with data or free bytes, depending upon the state of FIFO Transmit (FIFO

Transmit = “1”, alarm measures data bytes).

Table 14-36. FEC Rx FIFO Read Pointer Register

FEC Tx FIFO Read Pointer Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

READ[9:0]

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:21

—

Reserved

22:31

READ[9:0]

Read Pointer.

This pointer indicates the next location to be read by the FIFO controller.