32 rx fifo control (0x68)-rfcntl, 33 rx fifo alarm (0x6e)-rfalarm, Rx fifo control (0x68)—rfcntl -34 – Freescale Semiconductor MPC5200B User Manual

Page 550: Rx fifo alarm (0x6e)—rfalarm -34, Rx fifo control (0x68) -34, Rx fifo alarm (0x6e) -34, Rx fifo control (0x68)—rfcntl, Rx fifo alarm (0x6e)—rfalarm, Rfalarm, S the

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-39

15.2.32

Rx FIFO Control (0x68)—RFCNTL

15.2.33

Rx FIFO Alarm (0x6E)—RFALARM

Bit

Name

Description

0:3

—

Reserved

4:7

Frame[3:0]

Frame indicator. Not applicable to PSC FIFO’s, since the PSCs do not recognize frame

formats in the serial data stream.

8

—

Reserved

9

Error

FIFO error. A FIFO error has occurred due to either underflow, overflow, or read or write

pointer out of bounds.This bit is cleared by writing a ‘1’ to it.

10

UF

Underflow. The read pointer has surpassed the write pointer due to the FIFO having been

read when it contained no data. This bit is cleared by writing a ‘1’ to it.

11

OF

Overflow. The write pointer has surpassed the read pointer due to the FIFO having been

written when it was already completely full of data. This bit is cleared by writing a ‘1’ to it.

12

FR

Frame ready. Not applicable to PSC FIFO’s, since the PSCs do not recognize frame

formats in the serial data stream.

13

FULL

Full. The FIFO is completely full of data.

14

ALARM

The FIFO is requesting service from either BestComm or CPU. See

for a detailed description.

15

EMPTY

FIFO Empty. The FIFO is completely empty.

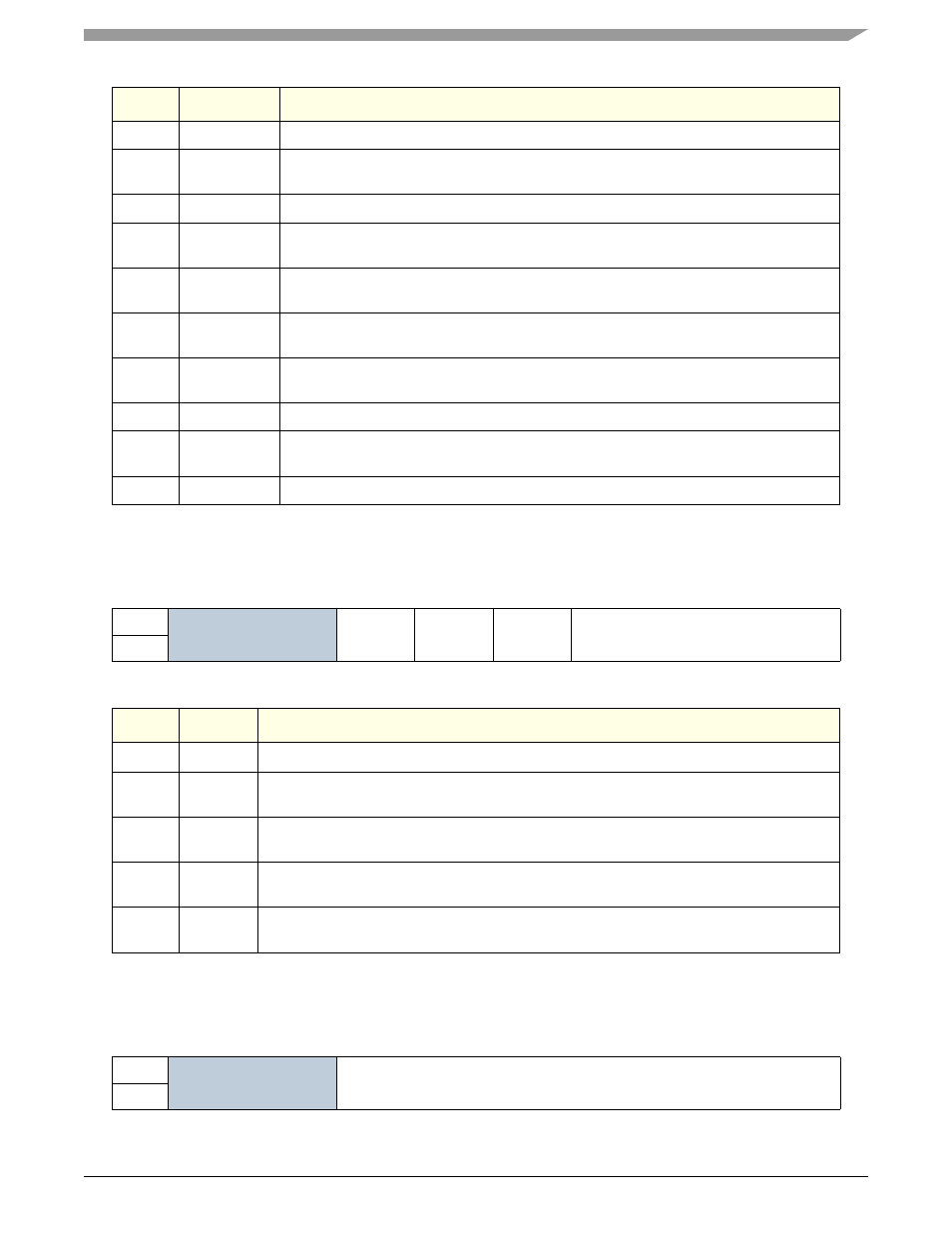

Table 15-60. Rx FIFO Control (0x68)

msb 0

1

2

3

4

5

6

7 lsb

R

Reserved

WFR

COMP

FRAME

GR[2:0]

W

RESET:

0

0

0

0

1

0

0

1

Bit

Name

Description

0:1

—

Reserved

2

WFR

Write frame. Not applicable to PSC FIFOs, since the PSCs do not recognize frame formats in

the serial data stream.

3

COMP

Re-enable requests on frame transmission completion. Not applicable to PSC FIFOs, since

the PSCs do not recognize frame formats in the serial data stream.

4

FRAME

Frame mode enable. THIS BIT MUST BE CLEARED BY WRITING A ‘0’ TO IT, since the PSCs

do not recognize frame formats in the serial data stream.

5:7

GR[2:0]

Last transfer granularity. Amount of data remaining in the Rx FIFO at which the ALARM bit in

the status register will go low/inactive. See

for details.

Table 15-61. Rx FIFO Alarm (0x6E)

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 lsb

R

Reserved

ALARM

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0