Status register (0x04) for mir / fir mode -8, Status register (0x04) for other modes -8 – Freescale Semiconductor MPC5200B User Manual

Page 520

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-9

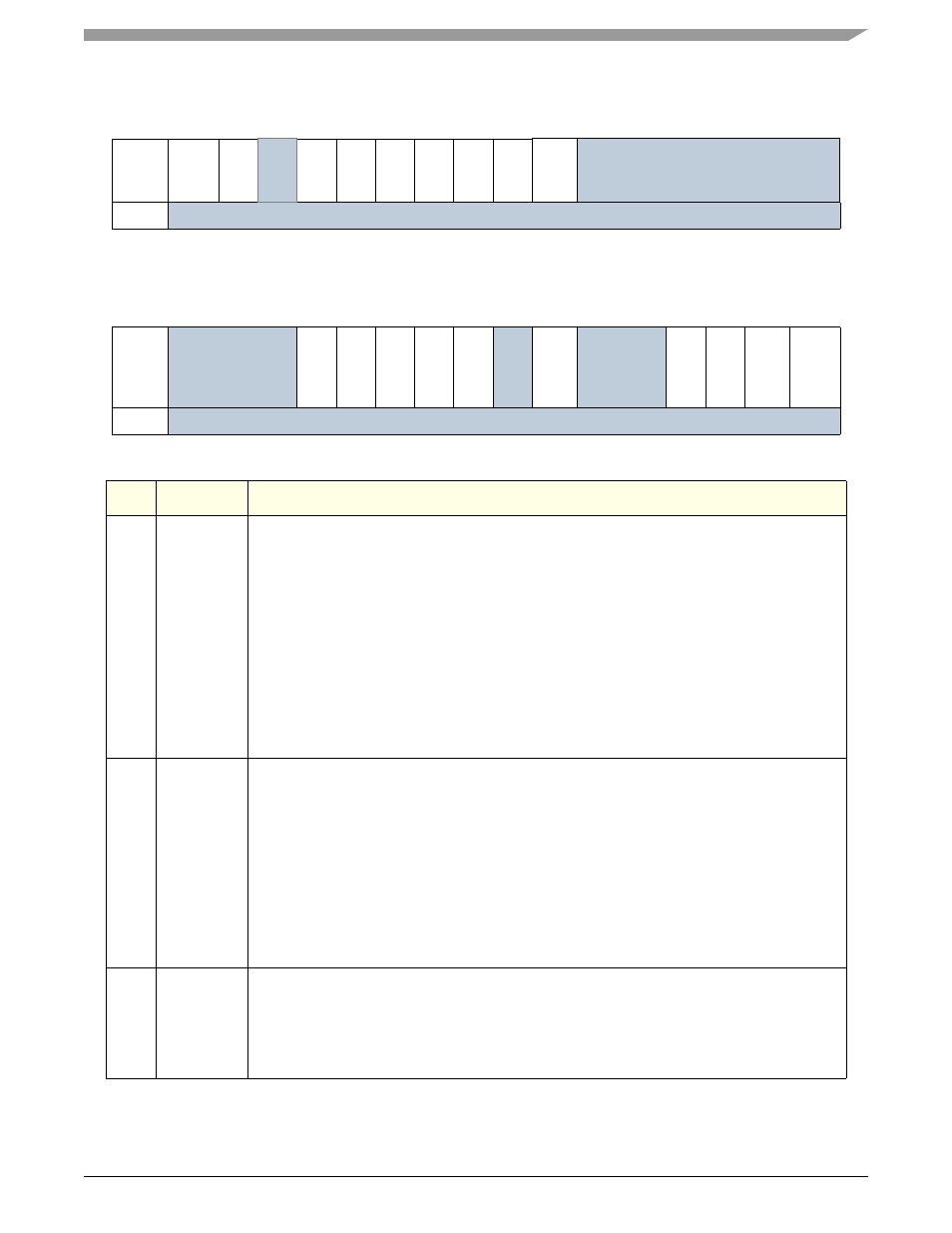

Table 15-12. Status Register (0x04) for MIR / FIR Mode

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 lsb

R

EOF

PH

Y

E

R

R

Reser

v

e

d

ORE

R

R

UR

E

R

R

Tx

RD

Y

FFU

LL

RxRD

Y

DEOF

Error

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Table 15-13. Status Register (0x04) for other Modes

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 lsb

R

Reserved

ORERR

URERR

Tx

R

D

Y

FF

U

L

L

RxRD

Y

Re

s

e

rv

e

d

Error

Reserved

CMD_SEND

DA

T

A

_

O

V

R

DA

T

A

_

V

A

L

ID

UNEX_R

X

_

SLO

T

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

0

RB/

EOF

UART / SIR —Received Break—detects breaks originating in middle of received character. Such

a break must persist until the end of next detected character time.

0 = No break received.

1 = An all-0 character of the programmed length was received without a stop bit. RB is valid

only when RxRDY = 1. Only a single FIFO position is occupied when a break is received.

Further entries to FIFO are inhibited until RxD returns to high state for at least one-half

bit-time, which equals two successive PSC

clock edges.

MIR / FIR—End of frame

0 = The next byte to be read from the RX-FIFO is not the last one of the frame.

1= The next byte to be read from the RX-FIFO is the last one of the frame. This bit is

effective when RxRDY=1.

other Modes—Reserved

1

FE/

PHYERR

UART / SIR—Framing Error— is not used (always 0) in Codec mode.

0 = No framing error occurred.

1 = No stop bit detected when corresponding FIFO data character received. Stop bit-check

occurs in middle of first stop bit position. FE is valid only when RxRDY=1.

MIR / FIR—Physical layer error

0 = No error

1 = In MIR mode, this denotes that the RX received an abort. In FIR mode, this denotes that

there was a decode error. This bit can be cleared by the reset error status command in the

CR.

other Modes—Reserved

2

PE

UART / SIR—Parity Error—valid only if RxRDY = 1. PE is not used (always 0) in Codec mode.

0 = No parity error occurred.

1 = If

[PM]=0x (with parity or force parity), corresponding FIFO character was received

with incorrect parity. If

[PM]=11 (multidrop), PE stores received A/D bit.\

other Modes—Reserved