4 transmitting and receiving in “normal” ac97 mode, Section 15.3.3.4, Transmitting and receiving in “normal” ac97 mode – Freescale Semiconductor MPC5200B User Manual

Page 575

MPC5200B Users Guide, Rev. 1

15-64

Freescale Semiconductor

PSC Operation Modes

Low-power mode can be left through either a warm or cold reset. The CPU does a warm reset by setting

[AWR] for at least 1µs. This

asserts the FRAME frame sync output in AC97 mode. The CPU does a cold reset in two steps:

1.

Writes 0 to whichever GPIO is being used as the active low AC97 reset pin for the minimum time specified in the AC97

specification.

2.

Writes 0 to PSC1 or PSC2

[ACRB]. CPU should set this bit after writing 1 to the GPIO used for the AC97 reset pin.

NOTE

Step 2 (above) is required so that the PSC knows when an AC97 cold reset is occurring.

15.3.3.4

Transmitting and Receiving in “Normal” AC97 Mode

When an AC97 Controller is specified (

[SIM]=0x3), PSC1 (or PSC2) begins receiving time slot 1 data, 1 bit-clock cycle after the rising

edge of frame sync, regardless of

[DTS1] value. However,

[SHDIR] must be 0, because the shift order must be msb first. The

PSC divides the bit-clock by 256 to generate a frame sync pulse that is high for 16-bit clock cycles. The transmitter sends 0s until the receiver

detects the Codec-ready condition (1 in the first bit of a new frame).

•

Until the receiver detects the Codec ready condition (1 in the first bit of a new frame), no data is put into the Rx FIFO for that frame.

•

When a Codec ready condition is detected, the receiver begins loading the Rx FIFO with the received time slot samples and

continues to do so until a 0 is received in the first bit of a new frame.

shows a AC97 interface timing diagram example. Because Rx data is sampled on the falling edge of the BitClk, for transmit

purposes, the frame has already started when the receiver detects a Codec-ready condition. For this reason, transmission starts at the next frame

sync after the Codec-ready condition is detected. The PSC stops transmission at the end of the frame in which the first bit of the received

frame is detected low (Codec not ready).

In the “normal” AC97 mode the controller never generate or analyze the Slot0,1 and Slot3 data, expect the Codec-ready bit in Slot0. In

opposite to the enhanced AC97 mode, see

Section 15.3.3.5, Transmitting and Receiving in “Enhanced” AC97 Mode.

Therefore all data slots

must be in the TxFIFO, for a complete frame must be 13 data words in the TxFIFO. The software must take sure that the data in the control

slots0,1 and 2 match the value in the data slots. For each AC97 slot a 32 bit data word must be in the TxFIFO. The receiver writes 13 32 bit

data words per AC97 frame to the RxFIFO.

Table 15-88

shows an example who to configure the PSC1 in AC97 mode.

15.3.3.5

Transmitting and Receiving in “Enhanced” AC97 Mode

To use PSC1 or PSC2 in “Enhanced” AC97 mode the bit

[EnAC97] and the

[SIM]=0x3 must be selected. The data transmission

is the standard AC97 one, see

Section 15.3.3.1, Block Diagram and Signal Definition for AC97 Mode

. But the AC97 controller is able to

generate the time slot0,1 and 2 data on the transmit site and will analyze received time slot0,1, and 2. Only during “Enhanced” AC97 mode

the registers

are used. In this mode, only the used data slots (3 to 12) are in the FIFOs.

The Rx_Slots field in the

register specify the expected RX data slots. If the received slots doesn’t match this specification the

receiver will ignore all data slots from the current frame and will set the

[UNEX_RX_SLOT] bit. Only the expected and valid tagged data

slots will be in the RxFIFO. This functionality guarantees that the software can assign the data in the RxFIFO to an AC97 slot. Only the order

in the RxFIFO mark the AC97 slot number.

The TX_Slots field in the

register define, which data slots will be send. All data for these slots must be in TxFIFO. The transmitter

generates the related slot0 tag data. If the TxFIFO is empty the transmitter will tag the frame as empty. The transmitter send data if the receiver

detect the “Codec ready state” for the current frame, the Tx FIFO contains the specified data words (defined in the

register) and

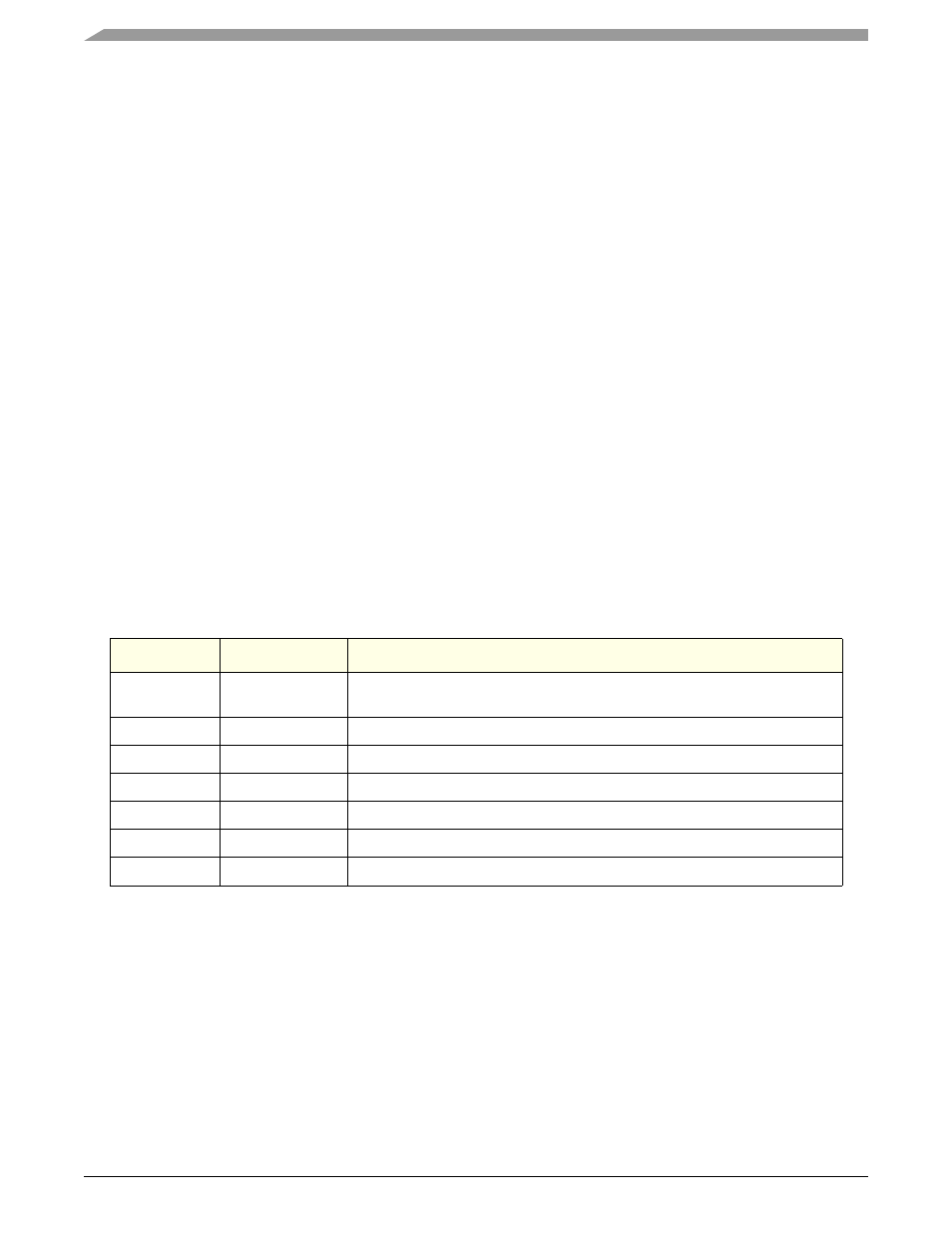

Table 15-88. General Configuration Example for “normal” AC97 Mode

Register

Value

Setting

0x0A

Disable the Tx and Rx part for configuration if the PSC was enabled by the work

before.

0x03000000

Select the AC97 mode

0x0XXX

Choose Rx FIFO “almost full” threshold level.

TFALARM

0x0XXX

Choose Tx FIFO “almost empty” threshold level.

0xXXXX

select the desired interrupt

Port_Config

0x00000030

Select the Pin-Muxing for AC97 mode PSC2, see

Chapter 2, Signal Descriptions

0x05

Enable Tx and Rx