11 pci arbiter register pciarb(rw) -mbar + 0x0d8c – Freescale Semiconductor MPC5200B User Manual

Page 319

MPC5200B Users Guide, Rev. 1

10-22

Freescale Semiconductor

Registers

10.3.2.10

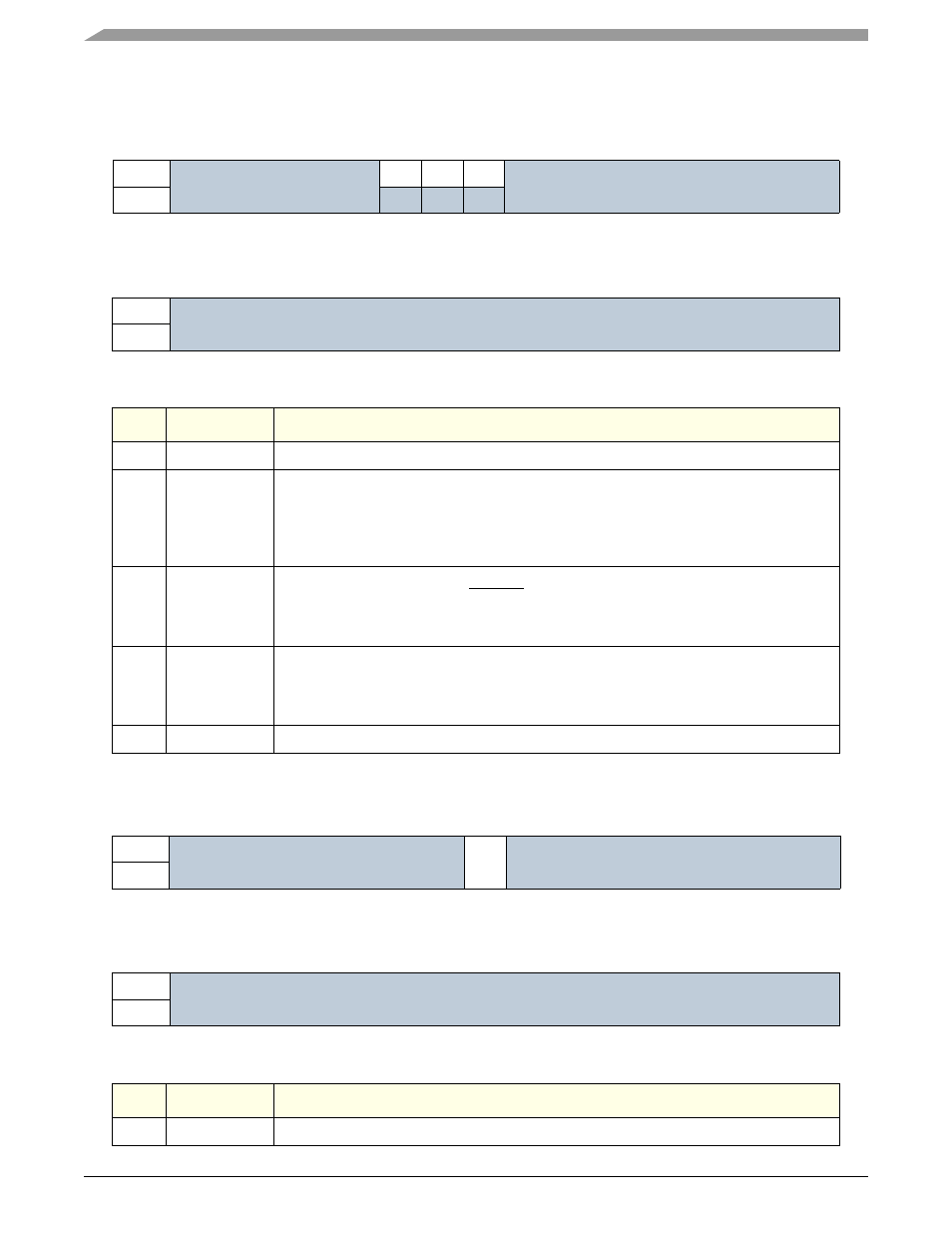

Initiator Status Register PCIISR(RWC) —MBAR + 0x0D88

10.3.2.11

PCI Arbiter Register PCIARB(RW) —MBAR + 0x0D8C

msb

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

RE

IA

TA

Reserved

W

rwc

rwc

rwc

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:4

Reserved

Unused bits. Software should write zero to this register.

5

Retry

Error

(RE)

This flag is set if Max_Retries is set to a finite value (0x01 through 0xff) and the Target has

performed Max_Retries number of retry disconnects for a single transaction. A retry error

would generally indicate a broken or improperly accessed Target. A CPU interrupt will be

generated if PCIICR[RE] bit is set. This is a RWC (Read/WriteClear) bit: to clear it, software

must write a ‘1’ at this position.

6

Initiator Abort

(IA)

This flag bit is set if the PCI controller issues an Initiator Abort flag. This indicates that no

Target responded by asserting DEVSEL within the time allowed for subtractive decoding. A

CPU interrupt will be generated if the PCIICR[IAE] bit is set. This is a RWC

(Read/WriteClear) bit: to clear it, software must write a ‘1’ at this position.

7

Target Abort

(TA)

This flag bit is set if the addressed PCI Target has signalled an Abort. A CPU interrupt will

be generated if the PCIICR[TAE] bit is set. It is up to application software to query the

Target’s status register and determine the source of the error. This is a RWC

(Read/WriteClear) bit: to clear it, software must write a ‘1’ at this position.

8:31

Reserved

Unused bits. Software should write zero to this register.

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

ASR

Reserved

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:6

Reserved

Unused bits. Software should write zero to this register.