2 fec interrupt event register-mbar + 0x3004, Fec interrupt event register—mbar + 0x3004 -12, Fec interrupt event register -12 – Freescale Semiconductor MPC5200B User Manual

Page 477: Section 14-10, fec interrupt event register

MPC5200B Users Guide, Rev. 1

14-12

Freescale Semiconductor

FEC Registers—MBAR + 0x3000

14.5.2

FEC Interrupt Event Register—MBAR + 0x3004

When an event occurs that sets a bit in the IEVENT register, an interrupt is generated if the corresponding bit in the interrupt enable register

(IMASK) is also set. The IEVENT register bit is cleared if 1 is written to that bit position. A 0 write has no effect. A hardware reset clears

this register.

These interrupts can be divided into operational interrupts, transceiver/network error interrupts and internal error interrupts. Interrupts that

may occur in normal operation are:

•

GRA

•

TFINT

•

MII

Interrupts resulting from errors/problems detected in the network or transceiver are:

•

HBERR

•

BABR

•

BABT

•

LATE_COL

•

COL_RETRY_LIM

Interrupts resulting from FIFO errors are:

•

XFIFO_UN

•

XFIFO_ERROR

•

RFIFO_ERROR

Some error interrupts are independently counted in the MIB block counters. Software may choose to mask these interrupts, since the errors

are visible to network management via the MIB counters.

•

HBERR – IEEE_T_SQE

•

BABR – RMON_R_OVERSIZE (good CRC), RMON_R_JAB (bad CRC)

•

BABT – RMON_T_OVERSIZE (good CRC), RMON_T_JAB (bad CRC)

•

LATE_COL – IEEE_T_LCOL

•

COL_RETRY_LIM – IEEE_T_EXCOL

•

XFIFO_UN – IEEE_T_MACERR

Bits

Name

Description

0:15

FEC_ID

Value identifying the FEC

16:20

—

Reserved

21

DMA

DMA function is included in the FEC

0 = FEC does not include DMA (BestComm is the DMA engine)

22

FIFO

FIFO function included in the FEC

1 = FEC does include a FIFO

24:31

FEC_REV

Value identifies the FEC revision

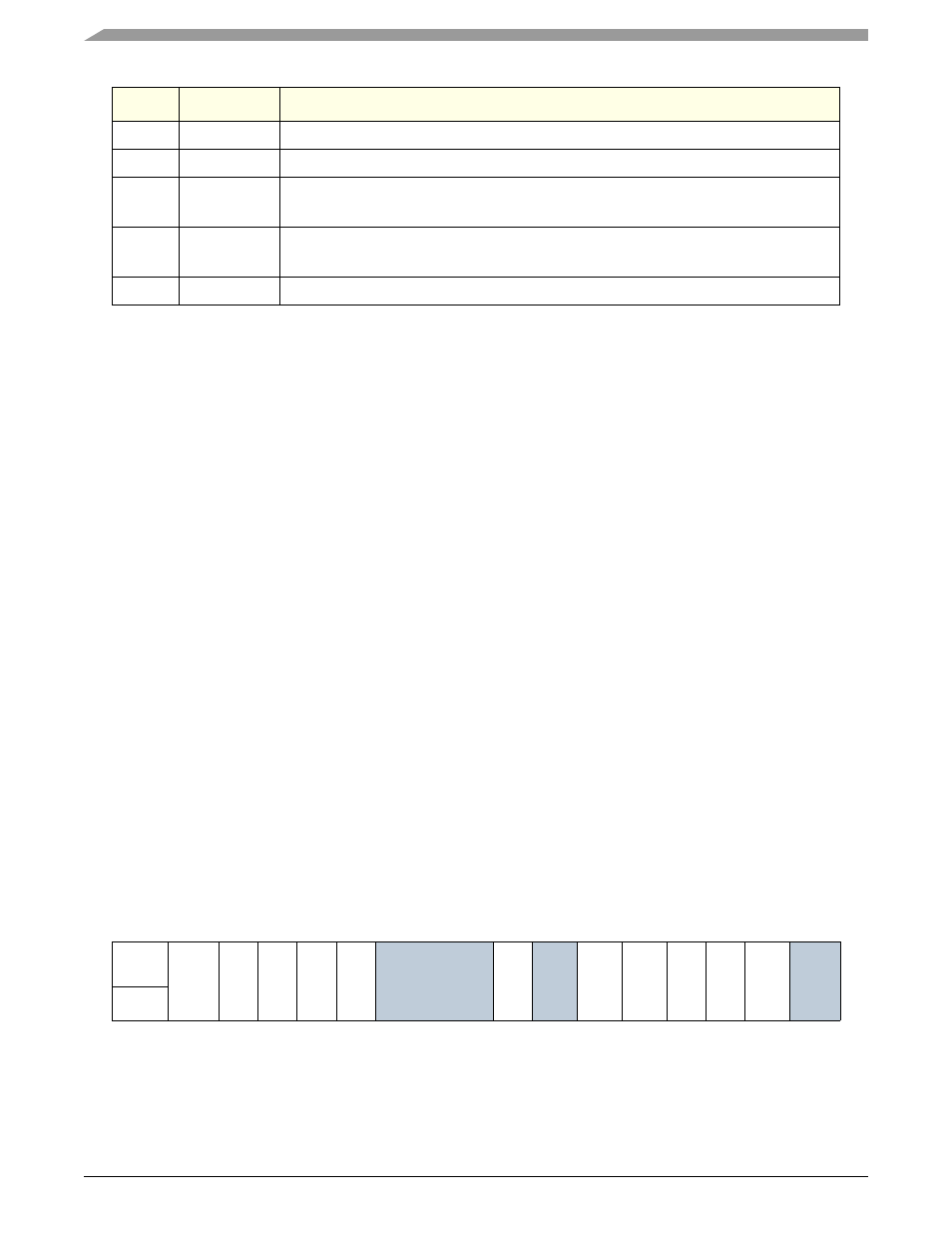

Table 14-10. FEC Interrupt Event Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

HB

E

R

R

BABR

BABT

GRA

TF

INT

Reserved

MII

Rsvd

LA

TE_COL

CO

L

_

RETR

Y_LIM

XFIFO

_

UN

XFIFO_

ERR

O

R

RFIF

O_

ERR

O

R

Rsvd

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0