25 infrared sir divide register (0x4c)-irsdr, Infrared sir divide register (0x4c)—irsdr -29, Infrared control 2 (0x48) for mir/fir modes -28 – Freescale Semiconductor MPC5200B User Manual

Page 545: Infrared control 2 (0x48) for other modes -28, Infrared sir divide register (0x4c)—irsdr, 25 infrared sir divide register (0x4c)—irsdr

MPC5200B Users Guide, Rev. 1

15-34

Freescale Semiconductor

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

15.2.25

Infrared SIR Divide Register (0x4C)—IRSDR

This register set the SIR pulse width. To set the SIR mode Baud rate see

Section 15.2.12, Counter Timer Upper Register (0x18)—CTUR

. This

register is reserved in other modes.

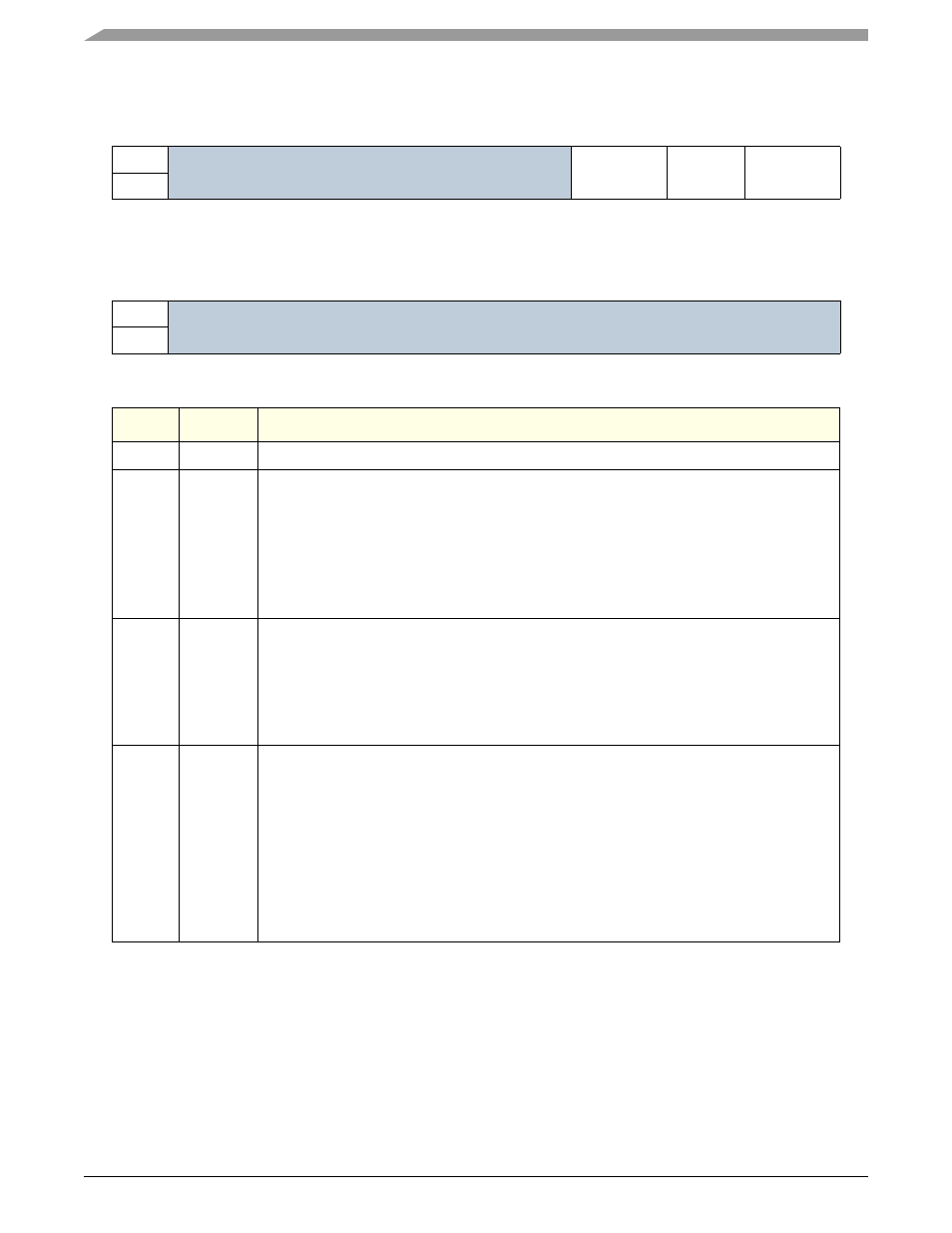

Table 15-47. Infrared Control 2 (0x48) for MIR/FIR Modes

msb 0

1

2

3

4

5

6

7 lsb

R

Reserved

SIPREQ

ABORT

NXTEOF

W

RESET:

0

0

0

0

0

0

0

0

Table 15-48. Infrared Control 2 (0x48) for other Modes

msb 0

1

2

3

4

5

6

7 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

Bit

Name

Description

0:4

—

Reserved

5

SIPREQ

MIR / FIR—Request to send SIP

0 = No operation

1 = If the TX becomes idle state, the TX starts to send one SIP pulse. This bit keeps high

until the TX finishes sending a SIP and becomes low automatically when the TX finishes

sending a SIP.

For more informations about the SIP pulse see also

other Modes—Reserved

6

ABORT

MIR / FIR— Abort output

0 = Stop sending abort sequence.

1 = While the TX is sending data or CRC, writing 1 to this bit causes the TX immediately

start to output abort sequence (2 or more illegal symbol “0000” in FIR mode, or 7 or more

consecutive 1 in MIR mode). Before the next frame is transmitted, this bit must be reset.

other Modes—Reserved

7

NXTEOF

SIR / MIR / FIR— Next is the last byte. This bit works independent form the mode. For other

modes which support the framing, like SPI, you can also use this bit to mark the last bit of

frame.

0 = The next write data is not the last byte in a frame.

1 = The next write data is the last byte in the current frame. When the processor performs

a write to the TB, an EOF mark is added to the data in the TX-FIFO memory. This bit is

cleared after writing to the transmit buffer. This bit is usually set by IP bus write operation.

During the CommBus transfer, the signal transmit done line indicate the end of frame,

therefore this bit is not used by the CommBus write operation.

other Modes—Reserved