Freescale Semiconductor MPC5200B User Manual

Page 522

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-11

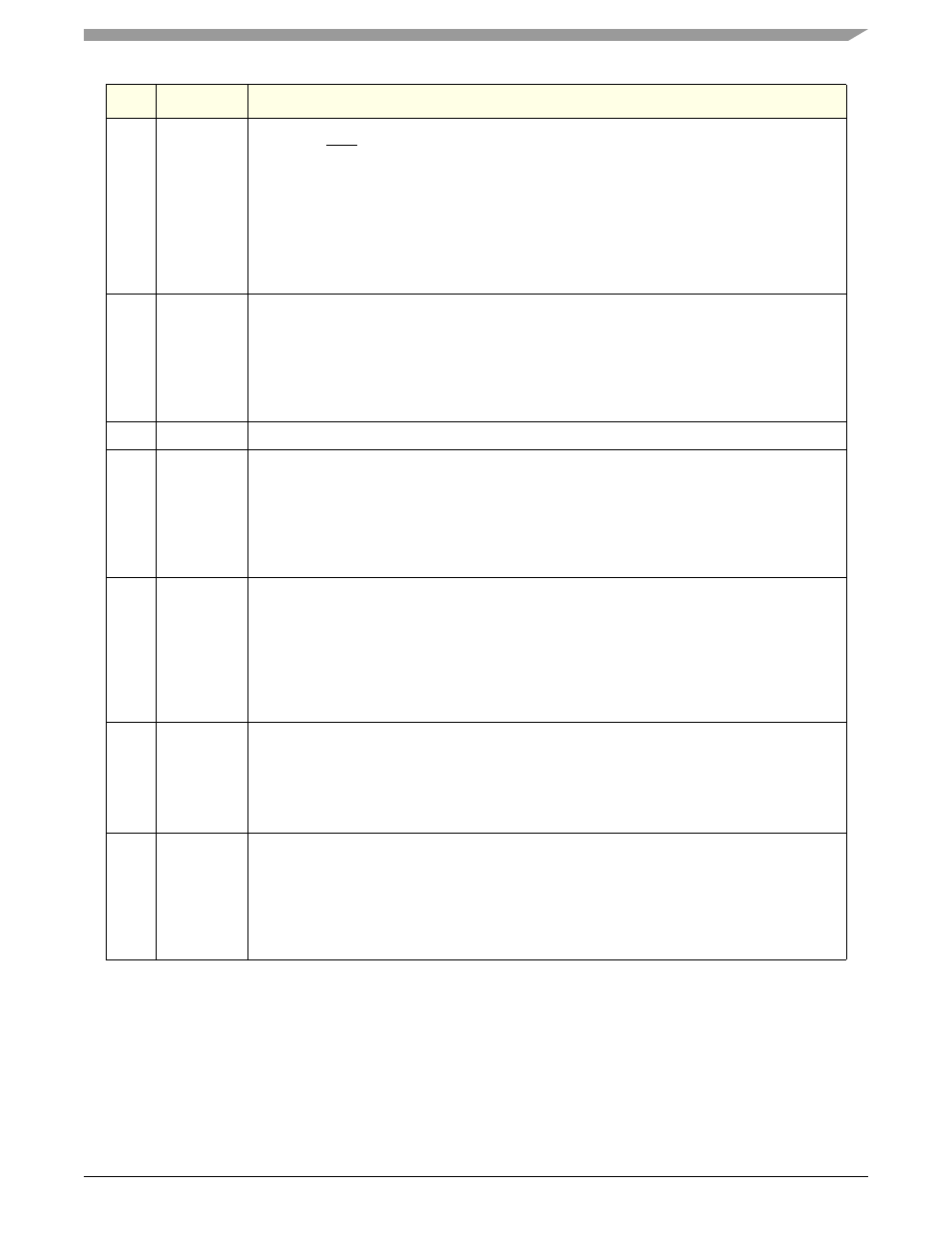

NOTE

The FIFO related status bits ORERR, URERR, RxRDY, FFUL and TxRDY will be changed only if

the peripheral (transmitter or receiver) access the FIFO. These bits reflect to the related bits in the

, therefore only the peripheral side can generate a FIFO access interrupt. The bits in the

register are also set. If the CPU side read from an empty FIFO or write to a full FIFO the

status bits in the

or

register will be set, but the status bit in the SR register are

unchanged. An access from the CPU side to the FIFO can’t generate an interrupt.

8

CDE

DEOF

UART—DCD Error

0 = The DCD input is negated while receiving data.

1 = No error

MIR / FIR—Detect End of Frame

0 = Rx did not receive an EOF after the last read

command.

1 = Rx received the EOF in the frame. In this case, the interrupt and request can be asserted

even if the Rx FIFO number is less than the threshold and

[1]=1.

other Modes—Reserved

9

Error

Error Status Detect

0 = The PSC controller detect no errors

1 = The PSC controller detect an error state. This error is a combination of the error bits: RB,

FE, PE,

URERR, ORERR from this register and RX and RX FIFO bit from the

register.

other Modes—Reserved

10:11

—

Reserved

12

CMD_SEND Enhanced AC97 Mode—Command Send ready

0 = The data in the

register was sent out by the AC97 transmitter

1= The data in the

register was not sent out. A write access to the

register set this bit to one. If the AC97 transmitter send out the CMD data then this bit was

cleared.

other Modes—Reserved

13

DATA_OVR

Enhanced AC97 Mode— Receive Status Data Overwrite

0 = No received status data overwrite.

1 = The received frame contains a new valid data status word in slot2, but the previous

received status data word was not read out before the new one was written to the

register. Therefore the old status data word was lost. A read access to the

register

cleared this bit

other Modes—Reserved

14

DATA_VALID Enhanced AC97 Mode—Received Status Data

0 = The received frame doesn’t contains valid status data.

1 = The received frame contains a valid data status word in slot2. The received data are

located in the

register. A read access to the

register cleared this bit.

other Modes—Reserved

15

UNEX_RX_

SLOT

Enhanced AC97 Mode—Unexpected Receive Slots detect

0 = The received frame contains only the slots which are defined in the

register or

a frame without AC97 data (frame is empty or contains only slot1 or slot2 data)

1 = The AC97 receive detect one or more slots which are not defined in the

register.

other Modes—Reserved

Bit

Name

Description