Bdlc analog round trip delay register -13 – Freescale Semiconductor MPC5200B User Manual

Page 692

Memory Map and Registers

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

20-13

READ: any time

WRITE: write once in normal and emulation modes.

Register functionality modified in special test mode.

Writes to unimplemented bits 7, 5 are ignored.

RXPOL

—

Receive Pin Polarity (Bit 6)

The Receive pin Polarity bit is used to select the polarity of incoming signal on the receive pin. Some external analog transceiver inverts the

receive signal from the J1850 bus before feeding back to the digital receive pin.

1 = Select normal/true polarity; true non-inverted signal from J1850 bus, i.e., the external transceiver does not invert the receive

signal.

0 = Select inverted polarity, where external transceiver inverts the receive signal.

BO4-BO0

—

BDLC Analog Roundtrip Delay Offset Field (Bits 4-0)

BO[4:0] adjust the transmitted symbol timings to account for the differing roundtrip delays found in different SAE J1850 analog transceivers.

The allowable delay range is from 0

µs to 31 µs, with a nominal target of 16 µs (reset value). Refer to

for the BO[4:0] values

corresponding to the expected transceiver delays and the resultant transmitter timing adjustment (in mux interface clock periods (t

bdlc

)). Refer

to the analog transceiver device specification for the expected roundtrip delay through both the transmitter and the receiver. The sum of these

two delays makes up the total roundtrip delay value.

NOTE

For Digital Loopback test, the Analog Roundtrip Delay Offset Field should be set to 0

µs.

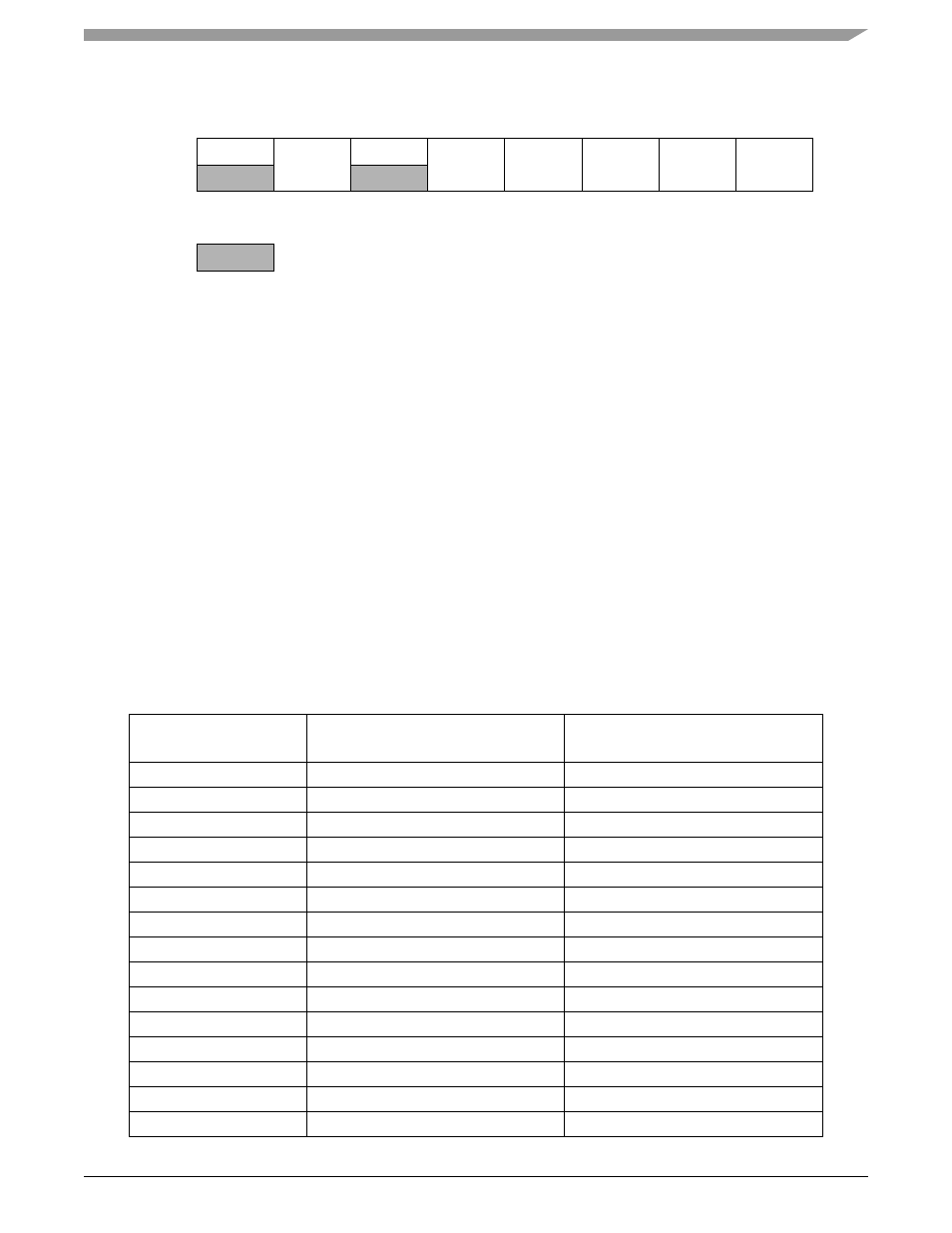

Table 20-6. BDLC Analog Round Trip Delay Register

msb 0

1

2

3

4

5

6

7 lsb

R

0

RXPOL

0

BO4

BO3

BO2

BO1

BO0

W

RESET:

0

1

0

1

0

0

0

0

= Unimplemented

Table 20-7. BARD Values vs. Transceiver Delay and Transmitter Timing Adjustment

BARD Offset Bits BO[4:0]

Corresponding Expected

Transceiver’s delays (

µ

s)

Transmitter Symbol Timing

Adjustment (

t

bdlc

)

1

00000

0

0

00001

1

1

00010

2

2

00011

3

3

00100

4

4

00101

5

5

00110

6

6

00111

7

7

01000

8

8

01001

9

9

01010

10

10

01011

11

11

01100

12

12

01101

13

13

01110

14

14