3 psc in ac97 mode, Bit spi slave mode for psc2 -53, Ac97 mode see – Freescale Semiconductor MPC5200B User Manual

Page 572: Section 15.3.3, psc in ac97 mode

PSC Operation Modes

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-61

shows an example how to configure the PSC2 as SPI slave.

•

use PSC2 as SPI slave

•

8bit data

•

clock is active low, CPOL = 0;

•

the first SCK edge is issued at the beginning of the data transfer; CPHA = 1

•

msb first

•

set the

TFALARM

level to 0x010, alarm occurs if 16 byte are in the TxFIFO

•

set the

level to 0x00C, alarm occurs if 12 byte space in the RxFIFO

•

enable TxRDY interrupt

15.3.3

PSC in AC97 Mode

After reset all PSCs are in UART mode. AC97 mode is chosen by setting the

[SIM] =0x3. The other

field should be initialized at

the same time. Only PSC1 and PSC2 support the AC97 mode. The AC97 controller supports two different AC97 modes, see

Transmitting and Receiving in “Normal” AC97 Mode

and

Section 15.3.3.5, Transmitting and Receiving in “Enhanced” AC97 Mode.

The

important register to configure the PSC for AC97 mode are:

•

register - select the Codec mode

•

TFALARM

- select the FIFO “Alarm” level

•

register - enable or disable receiver and transmitter

•

register - generate the reset pulse for the external device

•

Port_config - select the right Pin-Muxing, see

Chapter 2, Signal Descriptions

Port_Config

0x00000600

Select the Pin-Muxing for PSC3 Codec mode, see:

0x05

Enable Tx and Rx

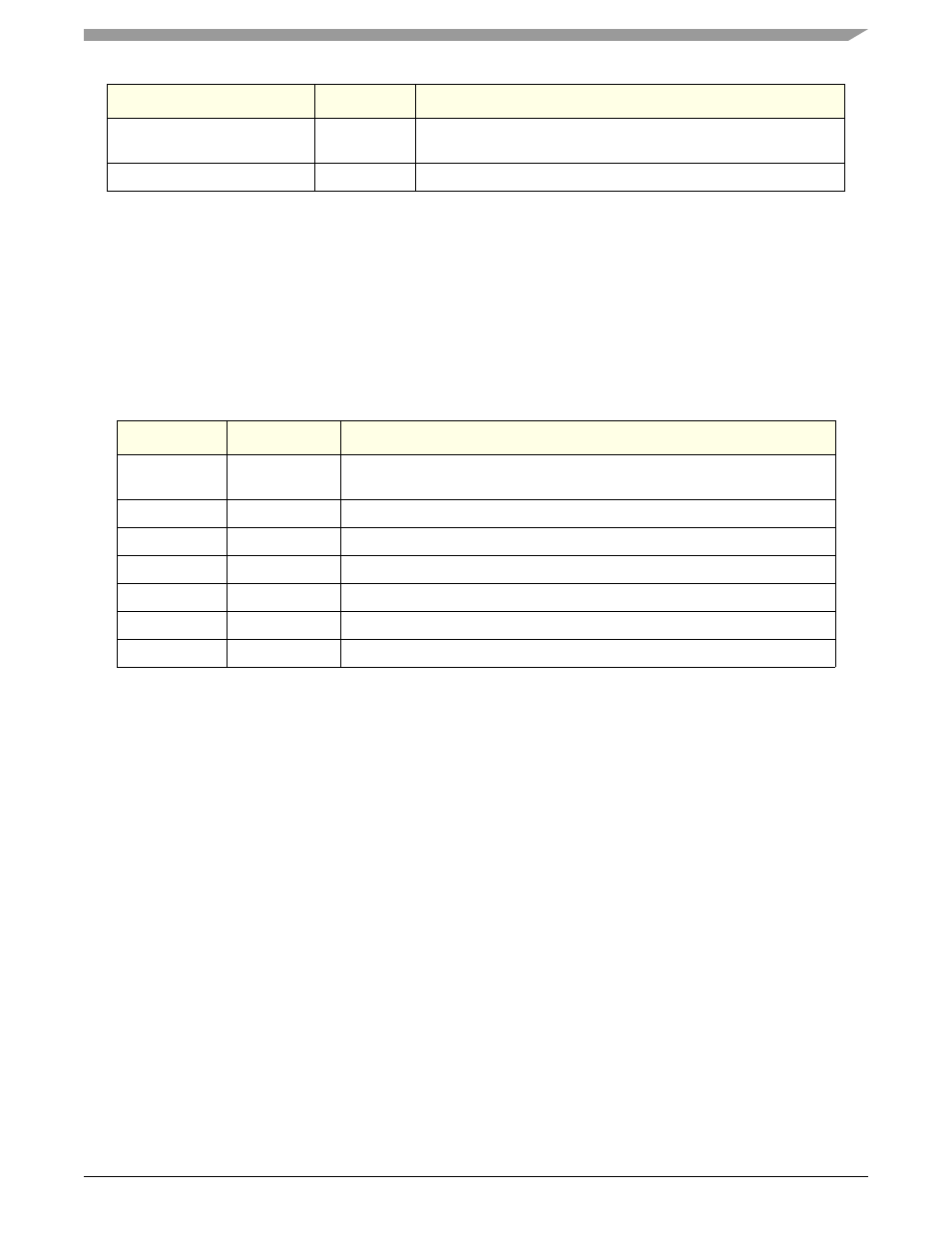

Table 15-86. 8-bit SPI Slave mode for PSC2

Register

Value

Setting

0x0A

Disable the Tx and Rx part for configuration if the PSC was enabled by the work

before.

0x01009000

Select the 8bit Codec SPI slave mode, msb first, CPOL = 0; CPHA = 1

0x000C

set the RFALARM level to 0x00C

TFALARM

0x0010

set the TFALARM level to 0x010

0x0100

enable TxRDY interrupt

Port_Config

0x00000060

Select the Pin-Muxing for PSC2 Codec mode, see

Chapter 2, Signal Descriptions

0x05

Enable Tx and Rx

Register

Value

Setting