Freescale Semiconductor MPC5200B User Manual

Page 660

Memory Map / Register Definition

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

19-21

READ: Anytime

WRITE: Anytime in initialization mode (INITRQ + 1 and INITAK = 1).

The identifier mask register specifies which of the corresponding bits in the identifier acceptance register are relevant for acceptance filtering.

•

To receive standard identifiers in 32-bit filter mode, the last three bits (AM[0:2]) in the following mask registers must be

programmed as "don’t care”:

— CANIDMR1

— CANIDMR5

•

To receive standard identifiers in 16-bit filter mode, the last three bits (AM[0:2]) in the following mask registers must be

programmed as "don’t care”:

— CANIDMR1

— CANIDMR3

— CANIDMR5

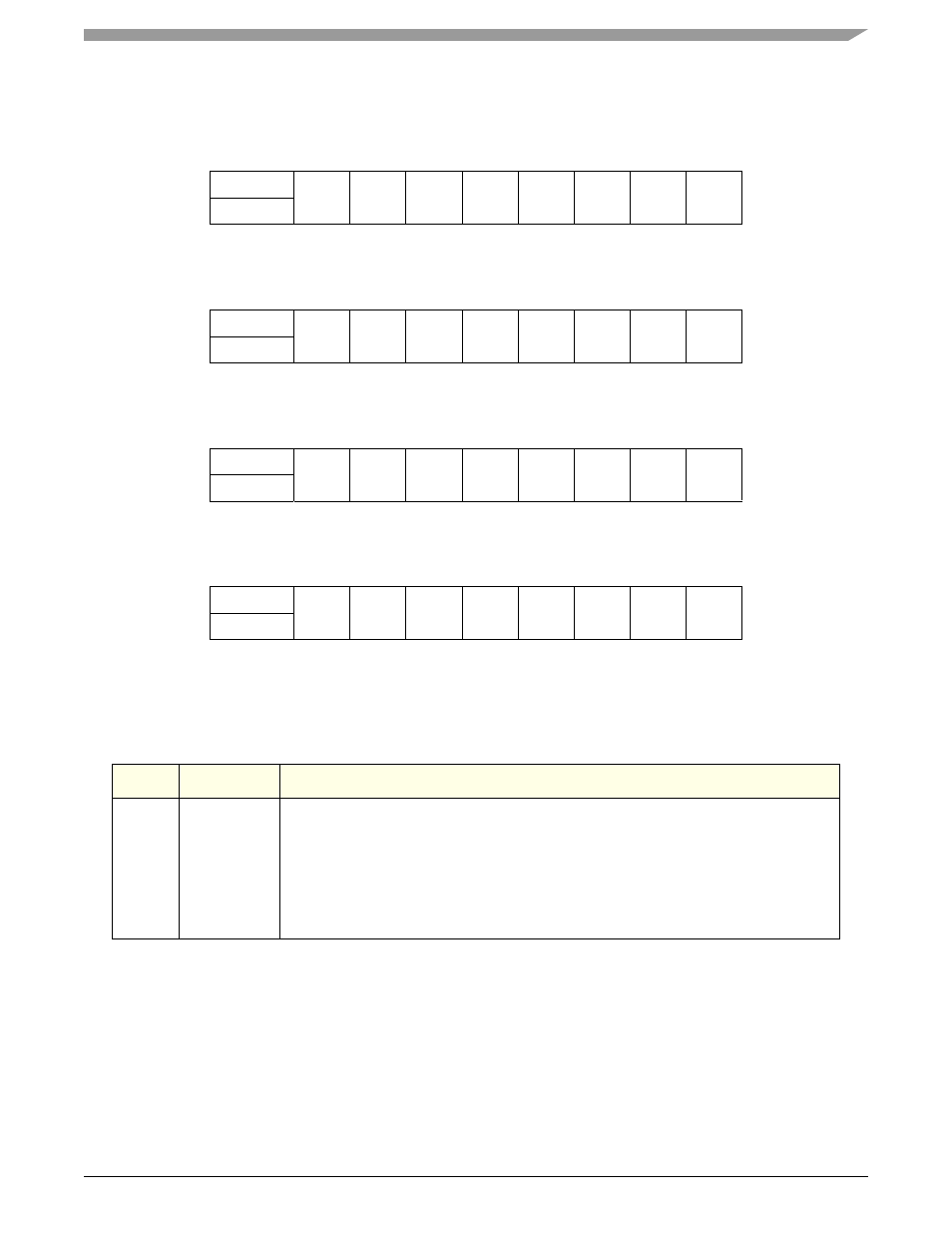

Table 19-25. MSCAN ID MaskRegisters (4 - 7)

msb 0

1

2

3

4

5

6

7 lsb

Adress Offset

0x938 / 0x9B8

CANIDMR4

R

AM7

AM6

AM5

AM4

AM3

AM2

AM1

AM0

W

RESET:

0

0

0

0

0

0

0

0

msb 0

1

2

3

4

5

6

7 lsb

Adress Offset

0x939 / 0x9B9

CANIDMR5

R

AM7

AM6

AM5

AM4

AM3

AM2

AM1

AM0

W

RESET:

0

0

0

0

0

0

0

0

msb 0

1

2

3

4

5

6

7 lsb

Adress Offset

0x93C / 0x9BC

CANIDMR6

R

AM7

AM6

AM5

AM4

AM3

AM2

AM1

AM0

W

RESET:

0

0

0

0

0

0

0

0

msb 0

1

2

3

4

5

6

7 lsb

Adress Offset

0x93D / 0x9BD

CANIDMR7

R

AM7

AM6

AM5

AM4

AM3

AM2

AM1

AM0

W

RESET:

0

0

0

0

0

0

0

0

Bit

Name

Description

0:7

AM[7:0]

Acceptance Mask bits—If a particular bit in this register is cleared, this indicates the

corresponding bit in the identifier acceptance register must be the same as its identifier bit

before a match is detected. The message is accepted if all such bits match. If a bit is set,

it indicates the state of the corresponding bit in the identifier acceptance register does not

affect whether or not message is accepted.

0 = Match corresponding acceptance code register and identifier bits

1 = Ignore corresponding acceptance code register bit