Interrupt mask register (0x14) for other modes -19 – Freescale Semiconductor MPC5200B User Manual

Page 532

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-21

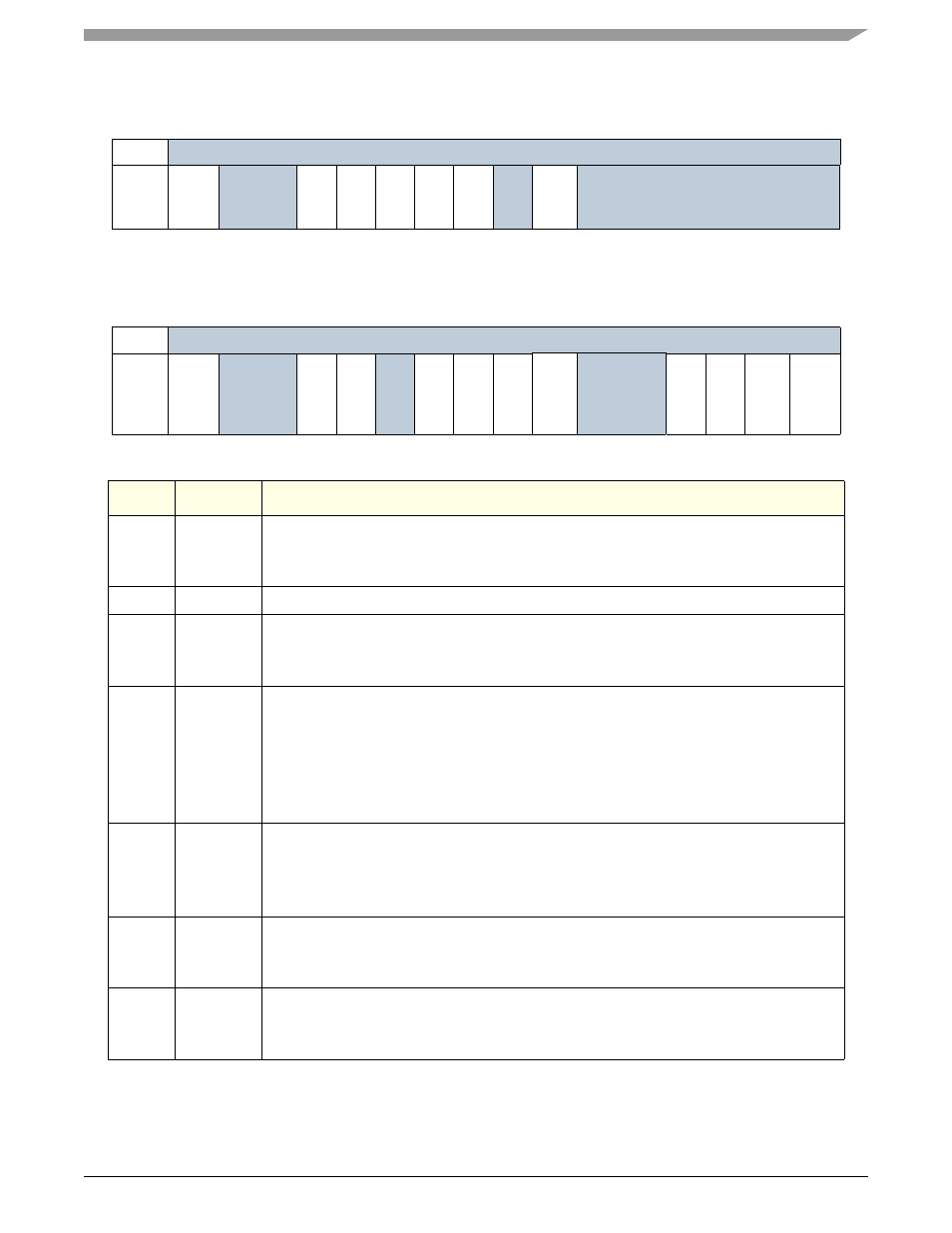

Table 15-28. Interrupt Mask Register (0x14) for UART / SIR Mode

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 lsb

R

Reserved

W

IPC

Reserved

ORERR

Tx

EMP

DB

RxRD

Y

FF

U

L

L

Tx

R

D

Y

Re

s

e

rv

e

d

Error

Reserved

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Table 15-29. Interrupt Mask Register (0x14) for other Modes

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 lsb

R

Reserved

W

IPC

Reserved

ORERR

URERR

Reser

v

ed

Rx

R

D

Y

FF

ULL

Tx

RD

Y

DE

OF

Error

Reserved

CMD_SEND

DA

T

A

_

O

V

R

DA

T

A

_

V

A

L

ID

UNEX_RX_

SLO

T

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

0

IPC

Input port change interrupt.

0 = IPC has no effect on the interrupt.

1 = Enable the interrupt for IPC in the ISR register.

1 :2

—

Reserved

3

ORERR

Overrun Error

0 =

ORERR has no effect on the interrupt.

1 = Enable the interrupt for

ORERR

4

TxEMP/

URERR

UART / SIR—TxEMP

0 = TxEMP has no effect on the interrupt.

1 = Enable the interrupt for TxEMP

other Modes—Underrun Error.

0 = URERR has no effect on the interrupt.

1 = Enable the interrupt for URERR.

5

DB

UART / SIR —Delta Break

0 = DB has no effect on the interrupt.

1 = Enable the interrupt for DB

other Modes—Reserved

6

RxRDY

FFULL

Rx FIFO over threshold

0 = RxRDY/FFULL has no effect on the interrupt.

1 = Enable the interrupt for RxRDY/FFULL.

7

TxRDY

Transmitter ready

0 = TxRDY has no effect on the interrupt.

1 = Enable the interrupt for TxRDY