Section 9-22, lpc rx/tx fifo read pointer register – Freescale Semiconductor MPC5200B User Manual

Page 296

Programmer’s Model

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

9-31

9.7.3.5

LPC Rx/Tx FIFO Read Pointer Register—MBAR + 0x3C50

9.7.3.6

LPC Rx/Tx FIFO Write Pointer Register—MBAR + 0x3C54

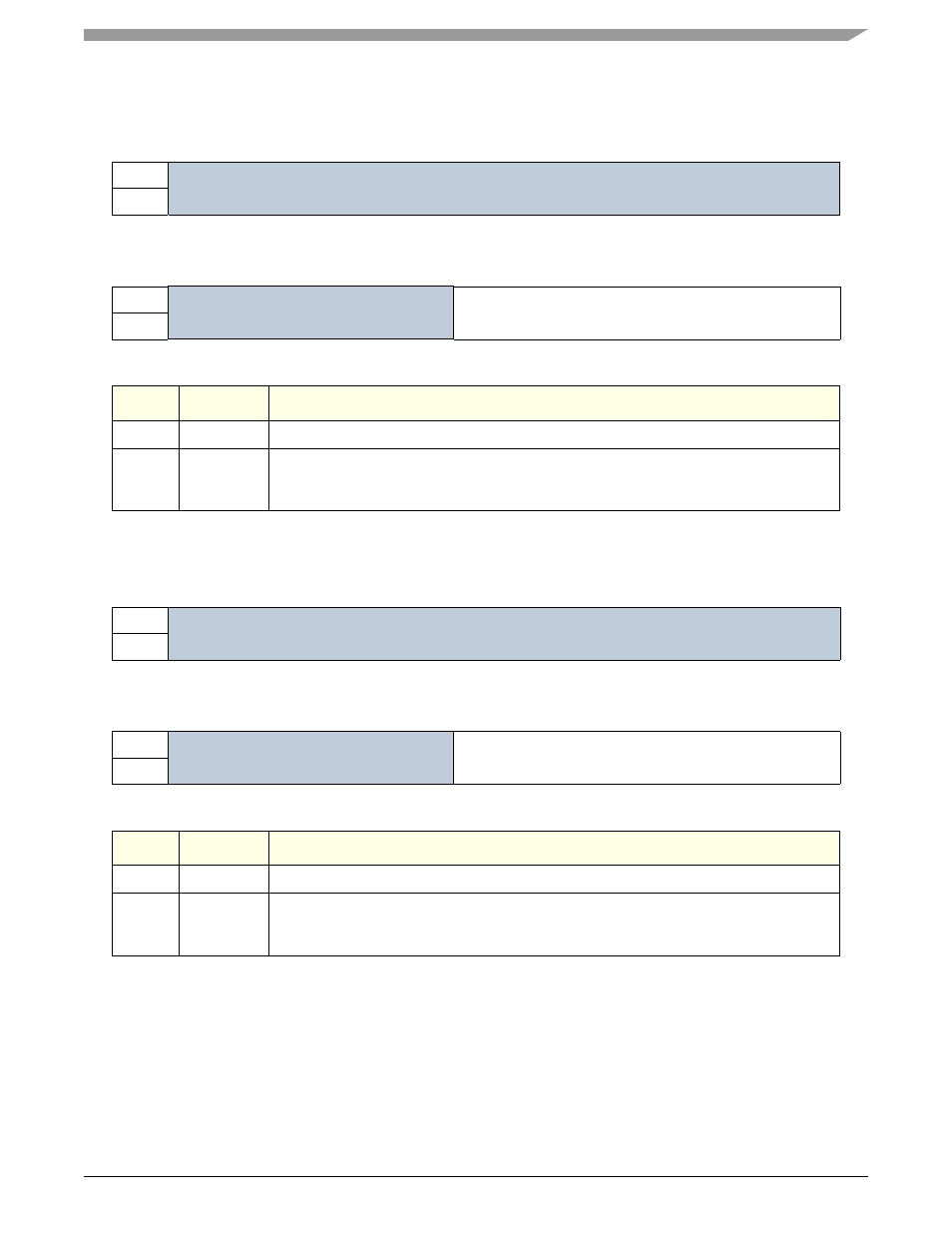

Table 9-22. LPC Rx/Tx FIFO Read Pointer Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

ReadPtr

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:22

—

Reserved

23:31

ReadPtr

Value is maintained by FIFO hardware and is NOT normally written. It can be adjusted in

special cases, but this disrupts data flow integrity. Value represents the Read address

presented to the FIFO RAM.

Table 9-23. LPC Rx/Tx FIFO Write Pointer Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

WritePtr

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:22

—

Reserved

23:31

WritePtr

Value is maintained by FIFO hardware and is NOT normally written. It can be adjusted in

special cases, but this disrupts data flow integrity. Value represents the Read address

presented to the FIFO RAM.