Freescale Semiconductor MPC5200B User Manual

Page 302

Registers

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

10-5

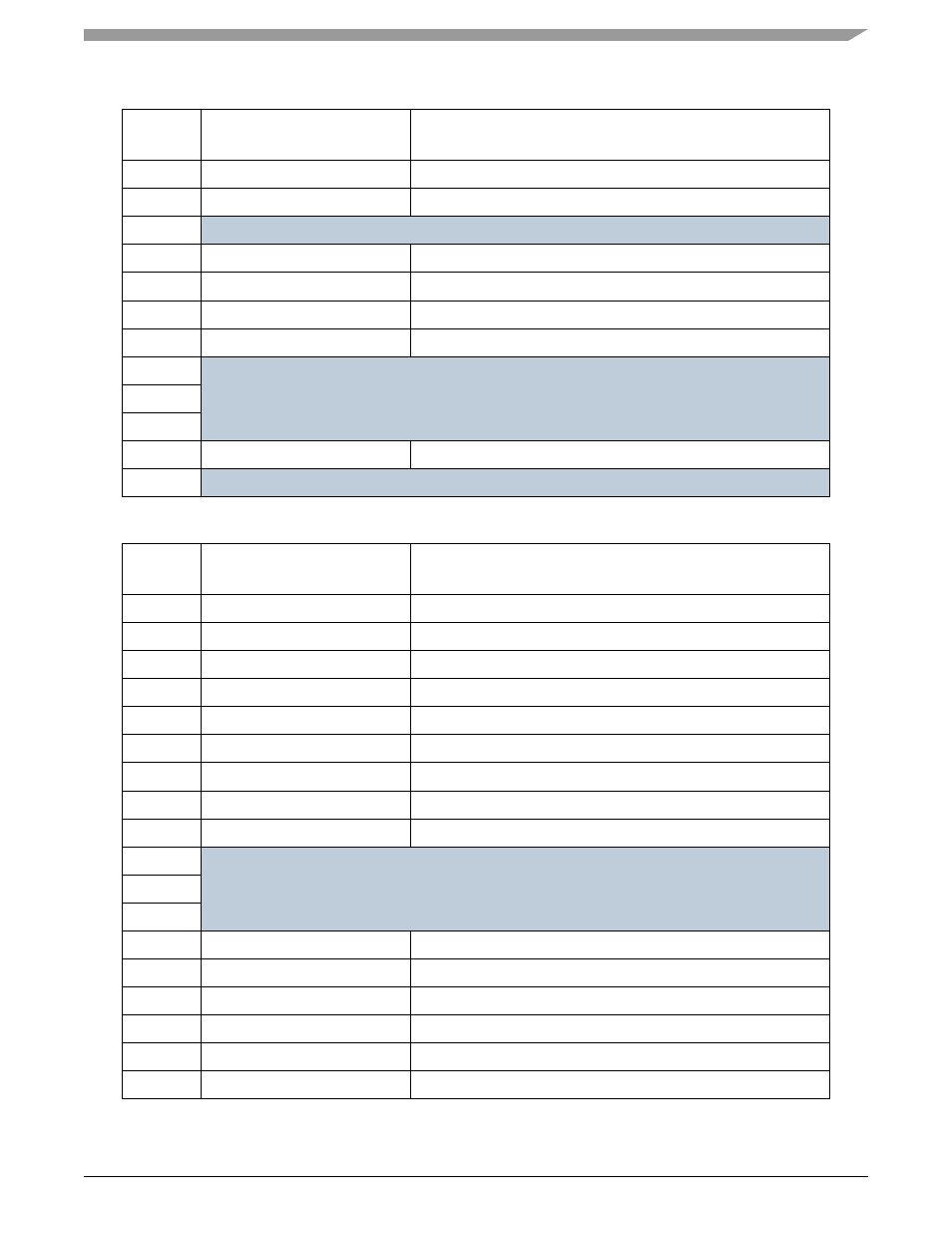

0x74

PCIIW1BTAR

Initiator Window 1 Base/Translation Address Register

0x78

PCIIW2BTAR

Initiator Window 2 Base/Translation Address Register

0x7C

Reserved

0x80

PCIIWCR

Initiator Window Configuration Register

0x84

PCIICR

Initiator Control Register

0x88

PCIISR

Initiator Status Register

0x8C

PCIARB

PCI Arbiter Register

0x90

Reserved

...

0xF4

0xF8

PCICAR

Configuration Address Register

0xFC

Reserved

Table 10-3. PCI Communication System Interface Register Map

Register

Offset

Mnemonic

Name

0x00

PCITPSR

Tx Packet Size

0x04

PCITSAR

Tx Start Address

0x08

PCITTCR

Tx Transaction Control Register

0x0C

PCITER

Tx Enables

0x10

PCITNAR

Tx Next Address

0x14

PCITLWR

Tx Last Word

0x18

PCITDCR

Tx Bytes Done Counts

0x1C

PCITSR

Tx Status

0x20

PCITPDCR

Tx Packets Done Counts

0x24

Reserved

...

0x3C

0x40

PCITFDR

Tx FIFO Data

0x44

PCITFSR

Tx FIFO Status

0x48

PCITFCR

Tx FIFO Control

0x4C

PCITFAR

Tx FIFO Alarm

0x50

PCITFRPR

Tx FIFO Read Pointer

0x54

PCITFWPR

Tx FIFO Write Pointer

Table 10-2. PCI Register Map (continued)

Register

Offset

Mnemonic

Name