Freescale Semiconductor MPC5200B User Manual

Page 658

Memory Map / Register Definition

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

19-19

READ: Anytime

WRITE: Anytime in initialization mode (INITRQ + 1 and INITAK = 1).

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria

in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0 to IDR3 registers of incoming messages in a bit-by-bit manner.

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1 and

CANIDMR0/1) are applied.

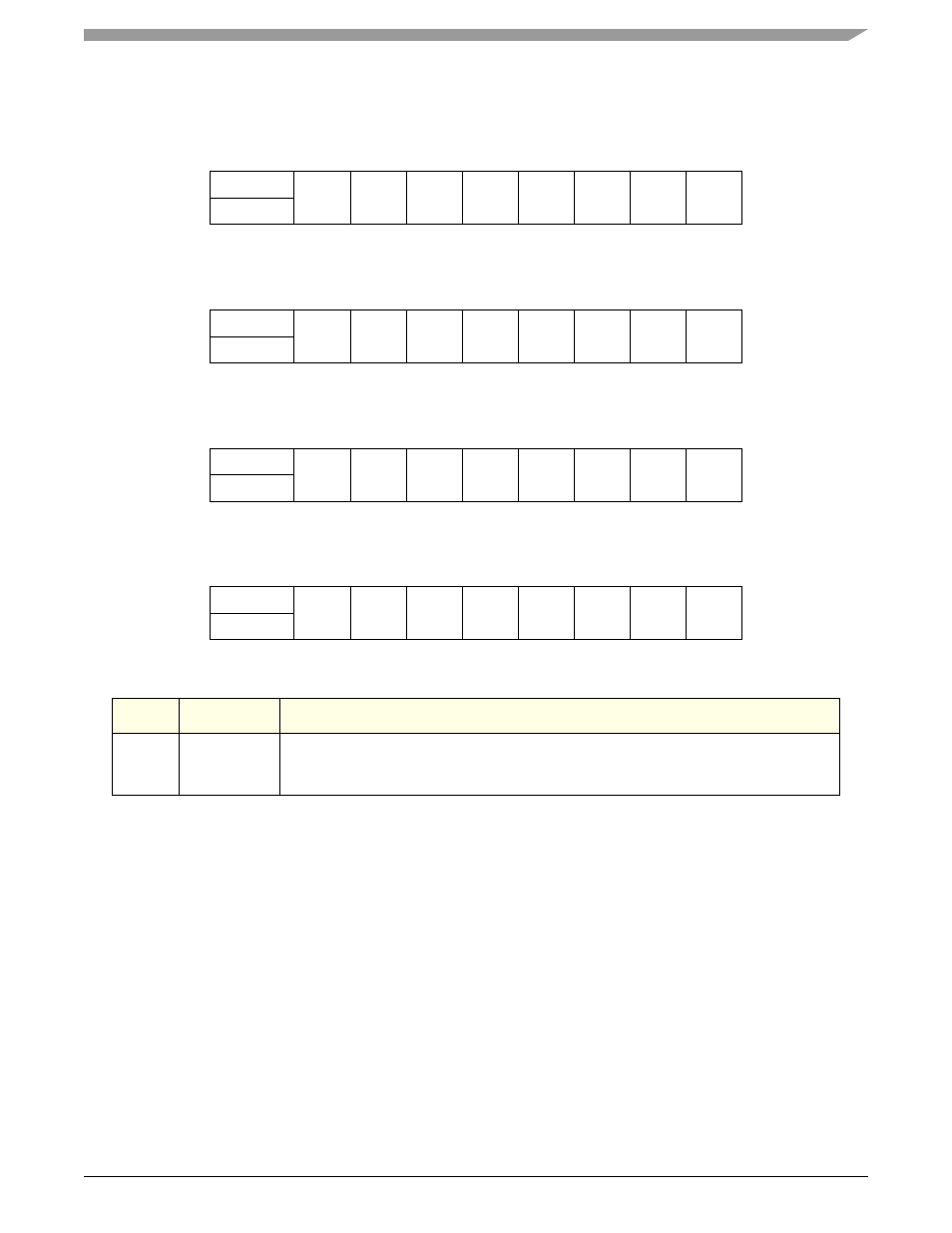

Table 19-23. MSCAN ID Acceptance Registers (4 - 7)

msb 0

1

2

3

4

5

6

7 lsb

Adress Offset

0x930 / 0x9B0

CANIDR4

R

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AC0

W

RESET:

0

0

0

0

0

0

0

0

msb 0

1

2

3

4

5

6

7 lsb

Adress Offset

0x931 / 0x9B1

CANIDR5

R

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AC0

W

RESET:

0

0

0

0

0

0

0

0

msb 0

1

2

3

4

5

6

7 lsb

Adress Offset

0x934 / 0x9B4

CANIDR6

R

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AC0

W

RESET:

0

0

0

0

0

0

0

0

msb 0

1

2

3

4

5

6

7 lsb

Adress Offset

0x935 / 0x9B5

CANIDR7

R

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AC0

W

RESET:

0

0

0

0

0

0

0

0

Bit

Name

Description

0:7

AC[7:0]

Acceptance Code—bits comprise a user defined sequence with which corresponding bits

of the related identifier register (IDRn) of the receive message buffer are compared. Result

of this comparison is then masked with the corresponding identifier mask register.