4 target abort, 5 latrule disable, 6 communication sub-system initiator interface – Freescale Semiconductor MPC5200B User Manual

Page 356: Table 10-12

Functional Description

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

10-59

10.4.5.4

Target Abort

A target abort will occur if the PCI address falls within a base address window (BAR0 or BAR1) that has not been enabled.

Target Base Address Translation Register 0 PCITBATR0(RW) —MBAR + 0x0D64

and

Section 10.3.2.3, Target Base Address

Translation Register 1 PCITBATR1(RW) —MBAR + 0x0D68

10.4.5.5

Latrule Disable

The latrule disable bit in the interface control register,

Section 10.3.2.4, Target Control Register PCITCR(RW) —MBAR + 0x0D6C

prevents the PCI controller from automatically disconnecting a target transaction due to the PCI 16/8 clock rule. With this bit set, it is possible

to hang the PCI bus if the internal bus does not complete the data transfer.

10.4.6

Communication Sub-System Initiator Interface

This interface provides for high-speed, autonomous DMA transactions to PCI with the PCI Controller operating as a standard Communication

Sub-System peripheral. Full duplex operation is supported and direct XL bus transactions can also be interleaved while CommBus

transactions are in progress. Internal arbitration will occur continuously to support transaction interleaving. (

.) Multi-Channel DMA operation operates independently of the XL bus. Non-PCI transactions on the XL bus will have 100%

bandwidth available to them during PCI Multi-Channel DMA activities. In general, this block will be used by functions in the Multi-Channel

DMA API.

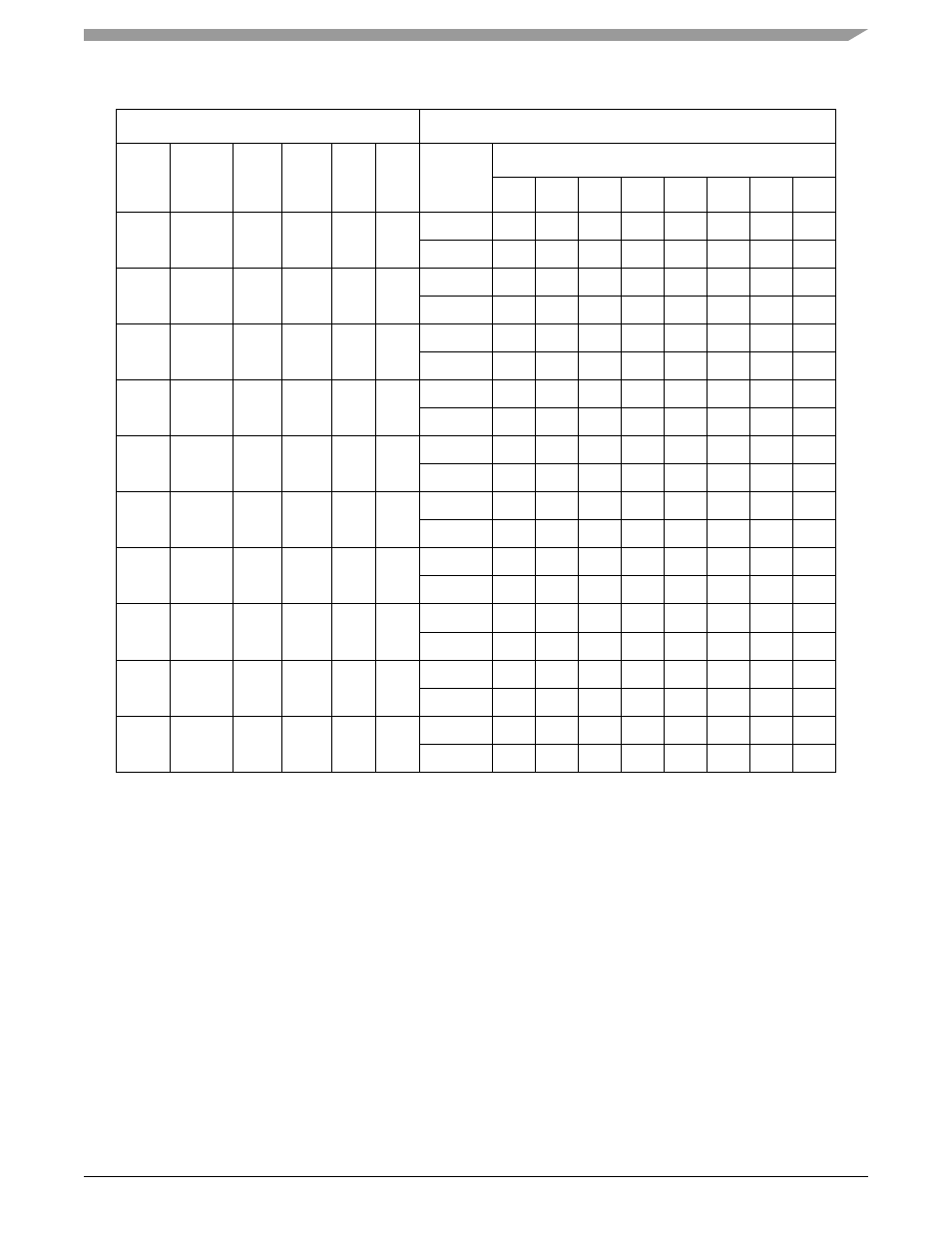

Table 10-12. Non-contiguous PCI to XL bus Transfers (require two XL Bus bus accesses)

PCI Bus

XL bus

BE

[3:0]

AD[2:0]

31:24

23:16

15:8

7:0

A[29:31]

Data Bus Byte Lanes

0

1

2

3

4

5

6

7

1010

000

OP3

OP2

000

OP2

010

OP3

1010

100

OP3

OP2

100

OP2

110

OP3

0110

000

OP3

OP2

000

OP2

011

OP3

0110

100

OP3

OP2

100

OP2

111

OP3

0101

000

OP3

OP2

001

OP2

011

OP3

0101

100

OP3

OP2

101

OP2

111

OP3

0010

000

OP3

OP2

OP1

000

OP1

010

OP2

OP3

0010

100

OP3

OP2

OP1

100

OP1

110

OP2

OP3

0100

000

OP3

OP2

OP1

000

OP1

OP2

011

OP3

0100

100

OP3

OP2

OP1

100

OP1

OP2

111

OP3