6 i2c interrupt control register-mbar + 0x3d20, C interrupt control register, C interrupt control register—mbar + 0x3d20 – Freescale Semiconductor MPC5200B User Manual

Page 634

I

2

C Interface Registers

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

18-17

18.3.6

I

2

C Interrupt Control Register—MBAR + 0x3D20

The Interrupt Control register is common to both MPC5200B I

2

C modules. Each module generates an internal interrupt that can be routed as

follows:

•

To the CPU interrupt, if IE is set to 1.

•

To the TX requestor at SDMA, if TE is set to 1.

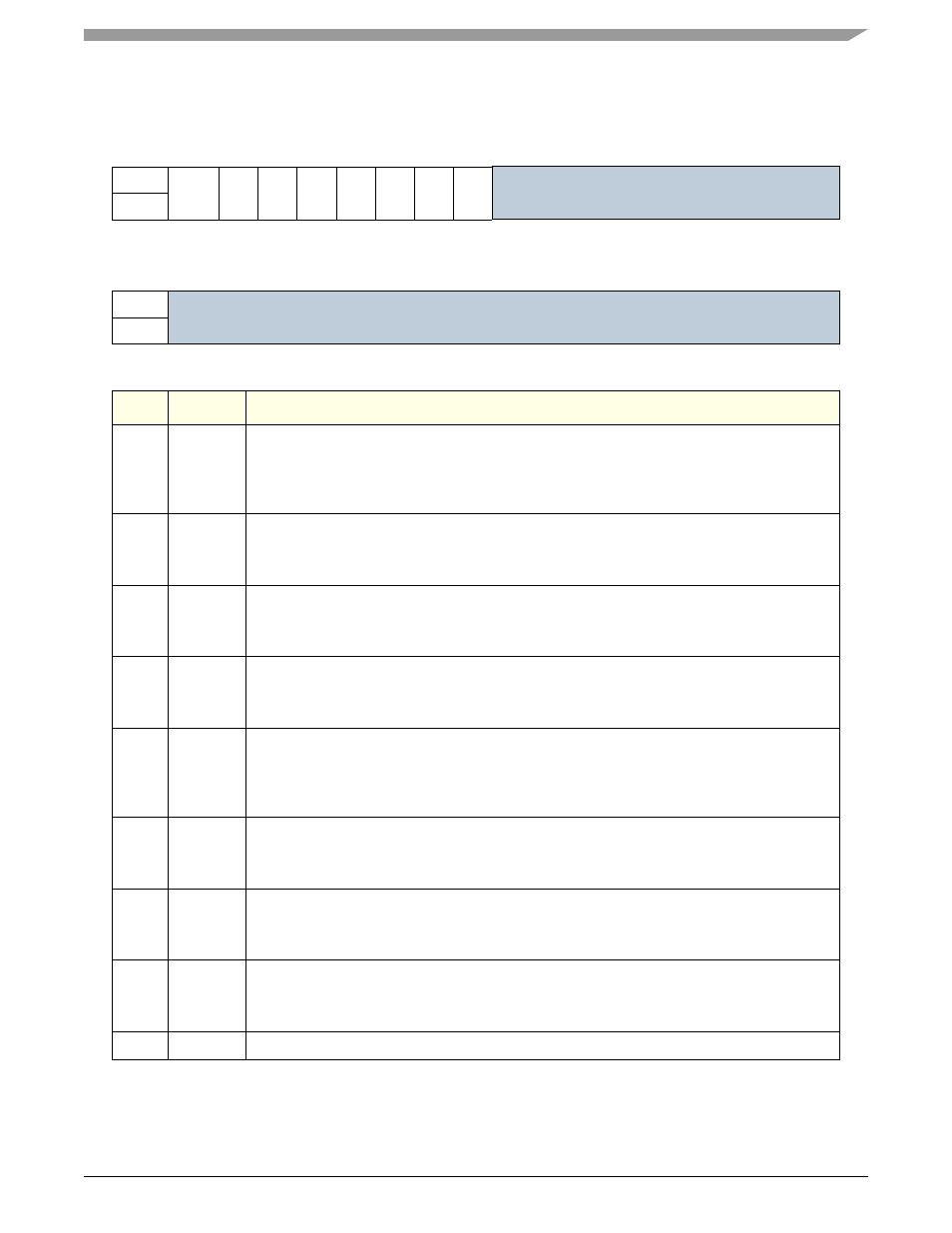

Table 18-8. I

2

C Interrupt Control Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

BNBE2

TE2

RE2

IE2

BNBE1

TE1

RE1

IE1

Reserved

W

RESET:

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

0

BNBE2

Bus Not Busy Enable 2—lets module 2 generate an interrupt when the bus is not busy. BNBE2

indicates an idle condition.

To clear the interrupt, software must write 0 to the bit position.

Reset condition disables BNBE2.

1

TE2

Transmit Enable 2—routes the interrupt for module 2 to the TX requestor at SDMA.

Clear by writing 0 to this bit position.

Reset condition disables TE2.

2

RE2

Receive Enable 2—routes the interrupt for module 2 to the RX requestor at SDMA.

Clear by writing 0 to this bit position.

Reset condition disables RE2.

3

IE2

Interrupt Enable 2—routes the interrupt for module 2 to the CPU.

Clear by writing 0 to this bit position.

Reset condition enables IE2.

4

BNBE1

Bus Not Busy Enable 1—lets module 1 generate an interrupt when the bus is not busy. BNBE1

indicates an idle condition.

To clear the interrupt, software must write 0 to the bit position.

Reset condition disables this bit.

5

TE1

Transmit Enable 1—routes the interrupt for module 1 to the TX requestor at SDMA.

Clear by writing 0 to this bit position.

Reset condition disables TE1.

6

RE1

Receive Enable 1—routes the interrupt for module 1 to the RX requestor at SDMA.

Clear by writing a 0 to this bit position.

Reset condition disables RE1.

7

IE1

Interrupt Enable 1—routes the interrupt for module 1 to the CPU.

Clear by writing 0 to this bit position.

Reset condition enables IE1.

8:31

—

Reserved