1 rx packet size pcirpsr(rw) -mbar + 0x3880, 2 rx start address pcirsar (rw) -mbar + 0x3884 – Freescale Semiconductor MPC5200B User Manual

Page 332

Registers

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

10-35

10.3.3.2.1

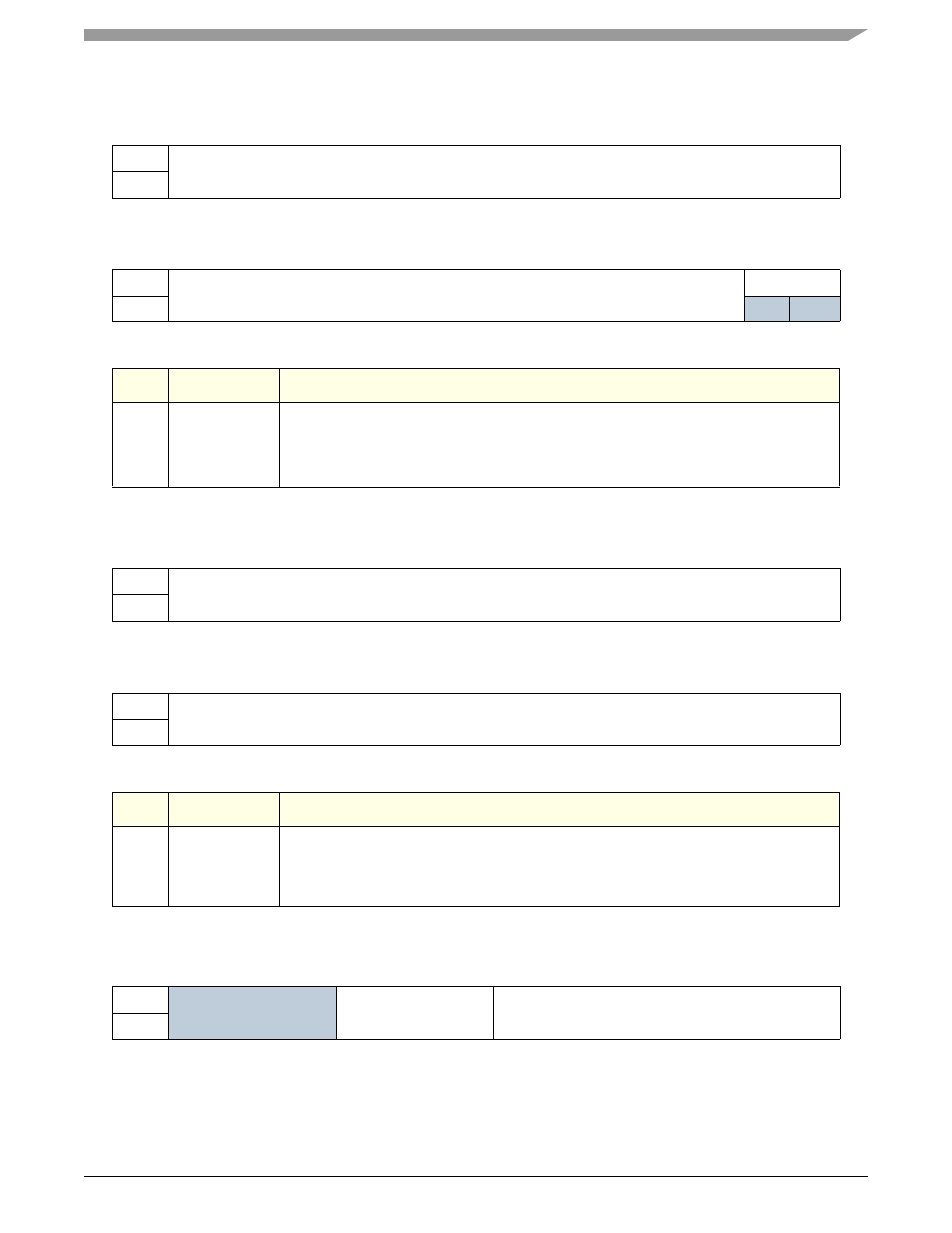

Rx Packet Size PCIRPSR(RW) —MBAR + 0x3880

10.3.3.2.2

Rx Start Address PCIRSAR (RW) —MBAR + 0x3884

10.3.3.2.3

Rx Transaction Control Register PCIRTCR(RW) —MBAR + 0x3888

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Packet_Size[31:16]

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Packet_Size[15:2]

Packet_Siz[1:0]

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:31

Packet_Size

The user writes this register with the number of bytes for Receive Controller to fetch over

PCI. The two low bits are hardwired low; only 32-bit data transfers to the FIFO are allowed.

Writing to this register also completes a Restart Sequence as long as Master Enable bit,

PCIRER[ME], is high and Reset Controller bit, PCIRER[RC], is low.

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Start_Add

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Start_Add

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:31

Start_Add

The user writes this register with the desired Starting Address for the current packet. This

is the address which will be first presented on the external PCI bus and then

auto-incremented as necessary. This register will not increment as the PCI packet

proceeds.

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

PCI_cmnd

Max_Retries

W

RESET

0

0

0

0

1100

0

0

0

0

0

0

0

0