See xlb arbiter configuration register – Freescale Semiconductor MPC5200B User Manual

Page 591

MPC5200B Users Guide, Rev. 1

16-4

Freescale Semiconductor

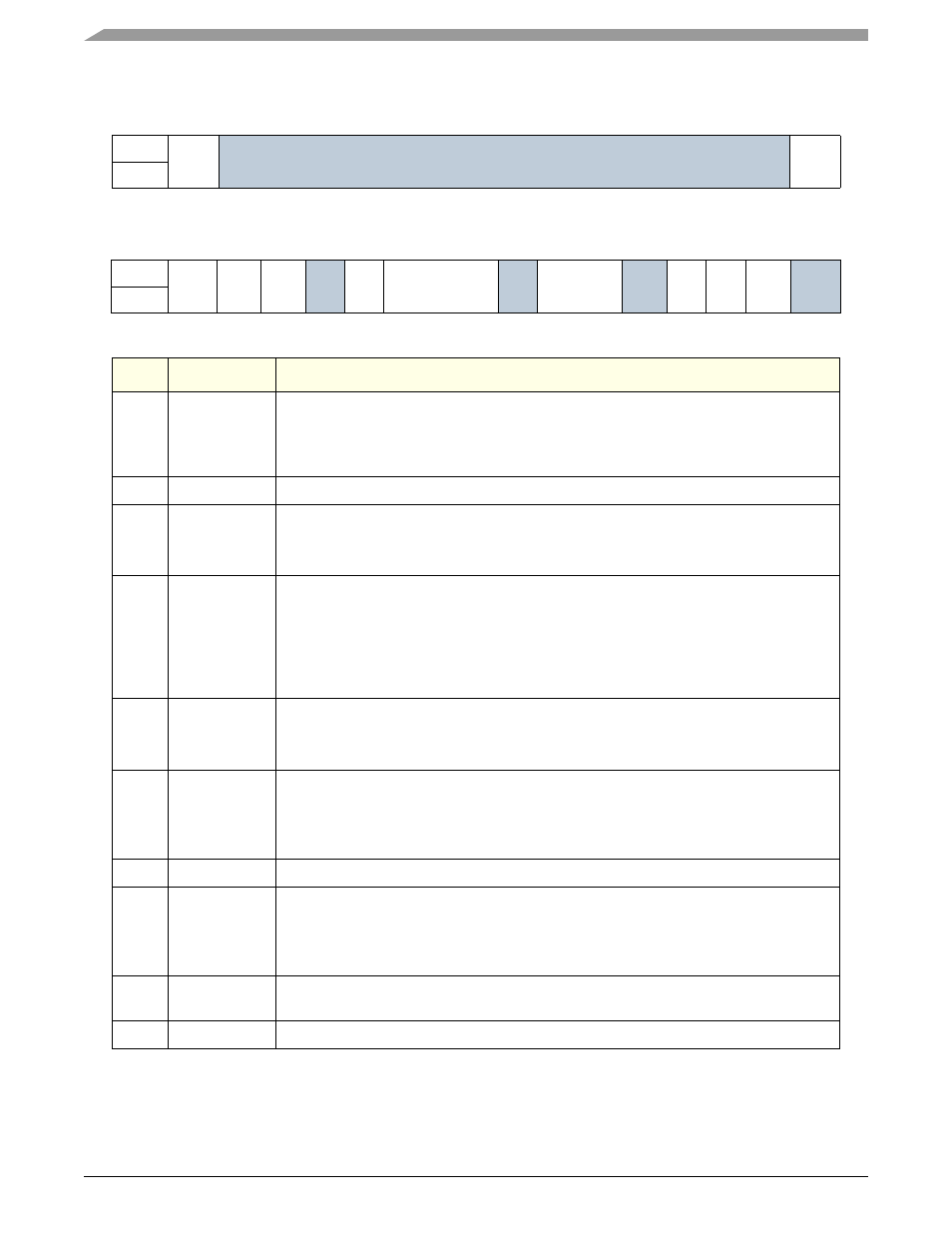

XLB Arbiter Registers—MBAR + 0x1F00

Table 16-1. Arbiter Configuration Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

PLDIS

Rsvd

BSDIS

W

RESET:

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

SE

USE_

WWF

TBEN Rsvd

WS

SP

Rsvd

PM

Rsvd

BA

DT

AT

Rsvd

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

Bit

Name

Description

0

PLDIS

Pipeline Disable. This bit is used to enable or disable transaction pipelining on the XLB. See

note below.

0 = Enable pipelining

1 = Disable pipelining

1:14

—

Reserved

15

BSDIS

BestComm Snooping Disable.

0 = BestComm XLB addresss snooping enabled.

1 = BestComm XLB addresss snooping disabled.

16

SE

Snoop Enable. This sets the address snooping enablement on the XLB.

0 = Disable address snooping. Internally on the XLB, the gbl_b signal is gated (always

negated). This overrides any setting of the

Arbiter Snoop Window Register (RW)—MBAR

.

1 = Allow address snooping. Internally on the XLB, the gbl_b signal is not gated, and

assertions of this signal during address tenures will be recognized.

17

USE_WWF

Force write-with-flush transfer type (TT) for PCI, BestComm, and USB interfaces to XLB.

0 = Write-with-kill operation is allowed on burst transactions.

1 = Always use write-with-flush on burst transactions.

18

TBEN

Timebase Enable. This bit is used as a “count enable” control input for the timebase counter

in the 603e core.

0 = Timebase should stop clocking.

1 = Timebase should continue clocking.

19

—

Reserved

20

WS

Minimum Wait State. This bit sets the minimum number of wait states for slaves to respond

with AACK assertion on the XLB.

0 = 0 minimum wait state.

1 = 1 minimum wait state.

21:23

SP[2:0]

Select Parked Master. These bits set the master that is used in Park on Programmed

Master mode (000 = master 0, 001 = master 1, ..., 111 = master 7).

24

—

Reserved