10 ata ultra dma timing 4 register-mbar + 0x3a24, Ata ultra dma timing 4 register – Freescale Semiconductor MPC5200B User Manual

Page 372

ATA Register Interface

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

11-7

11.3.1.10

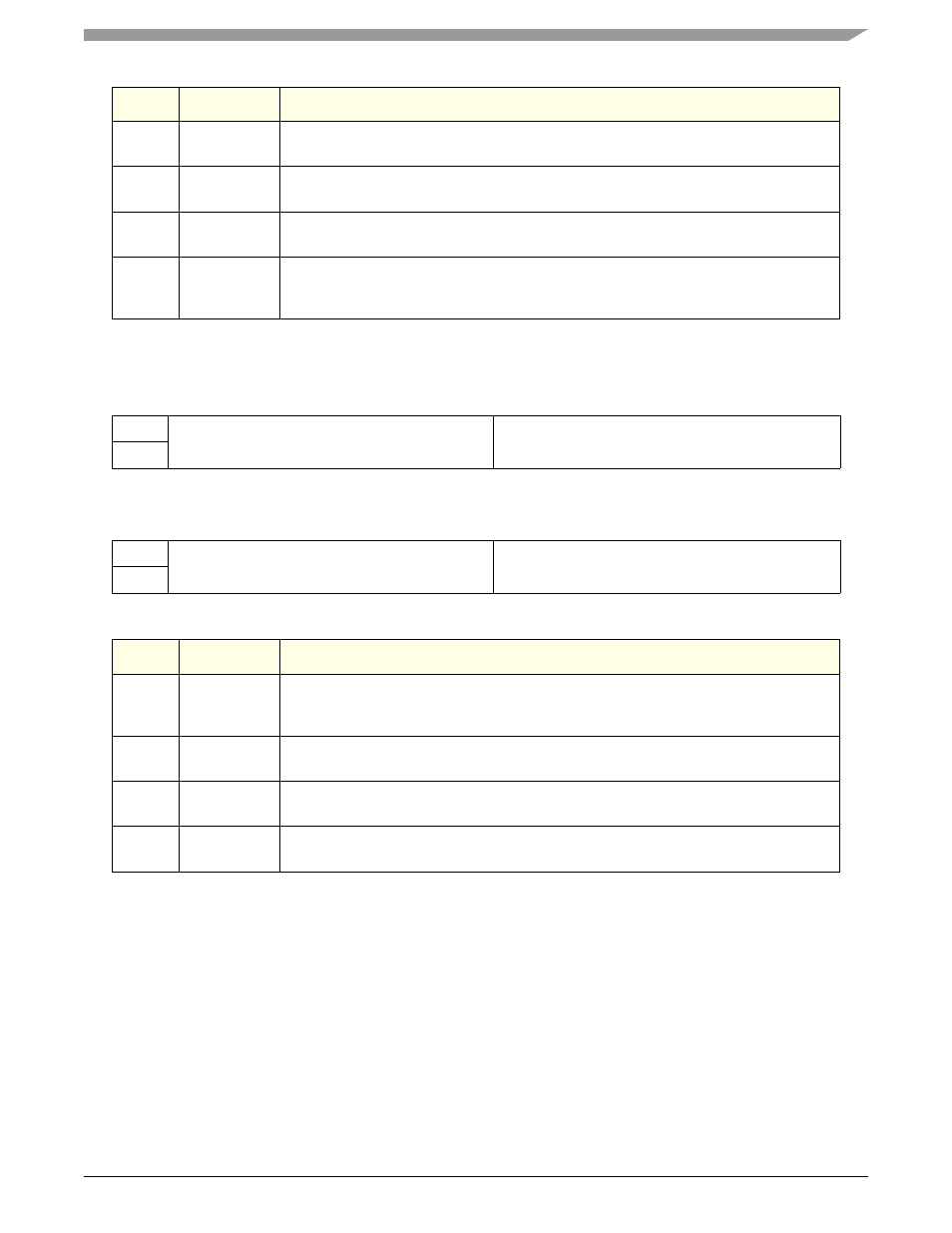

ATA Ultra DMA Timing 4 Register—MBAR + 0x3A24

Bits

Name

Description

0:7

udma_tmli

Limited interlock time with a defined minimum, when drive or host are waiting for response

from each other. Count value is based on system clock operating frequency.

8:15

udma_taz

Maximum time allowed for output drivers to release from being driven. Count value is

based on system clock operating frequency.

16:23

udma_tenv

Envelope time from DMACK to STOP and HDMARDY during data-out burst initiation.

Count value is based on system clock operating frequency.

24:31

udma_tsr

Strobe to DMARDY time. If DMARDY is negated before this long after strobe edge the

recipient receives no more than one additional data word. Count value is based on system

clock operating frequency.

Table 11-10. ATA Ultra DMA Timing 4 Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

udma_tss

udma_trfs

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

udma_trp

udma_tac

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:7

udma_tss

Time from strobe edge to negation of DMARQ (when drive terminates burst) or assertion

of STOP (when host terminates burst). Count value is based on system clock operating

frequency.

8:15

udma_trfs

Ready-to-final-strobe time. No strobe edges are sent this long after negation of DMARDY.

Count value is based on system clock operating frequency.

16:23

udma_trp

Ready-to-pause time. The time that recipient waits to initiate pause after negating

DMARDY. Count value is based on system clock operating frequency.

24:31

udma_tack

Setup and hold times for DMACK before negation or assertion. Count value is based on

system clock operating frequency.