Table 15-80 – Freescale Semiconductor MPC5200B User Manual

Page 565

MPC5200B Users Guide, Rev. 1

15-54

Freescale Semiconductor

PSC Operation Modes

•

FrameSync is low true

•

lsb first, transfer starts one cycle after the leading edge of FrameSync

•

set Mclk frequency to 33MHz

•

set Bitclk frequency to 250 KHz

•

FrameSync every 35 BitClk

•

set FrameSync width to 3 BitClk

•

set the

TFALARM

level to 0x010, alarm occurs if 16 byte are in the TxFIFO

•

set the

level to 0x00C, alarm occurs if 12 byte space in the RxFIFO

•

enable TxRDY interrupt

15.3.2.4

Transmitting and Receiving in ESAI Mode (Enhanced Serial Audio Interface)

The ESAI transmission is similar to the “Soft Modem” mode. Therefore the configuration is the same like described in

Transmitting and Receiving in “Soft Modem” Codec Mode.

The different is, that the ESAI protocol allow to transmit and receive more than

one data word per frame. To enable the ESAI mode the

[ESAI] bit must be set. The PSC calculate how many data words the transmitter

will send and how many data the receiver will expect.

Figure 15-10

shows the ESAI transmission diagram

.

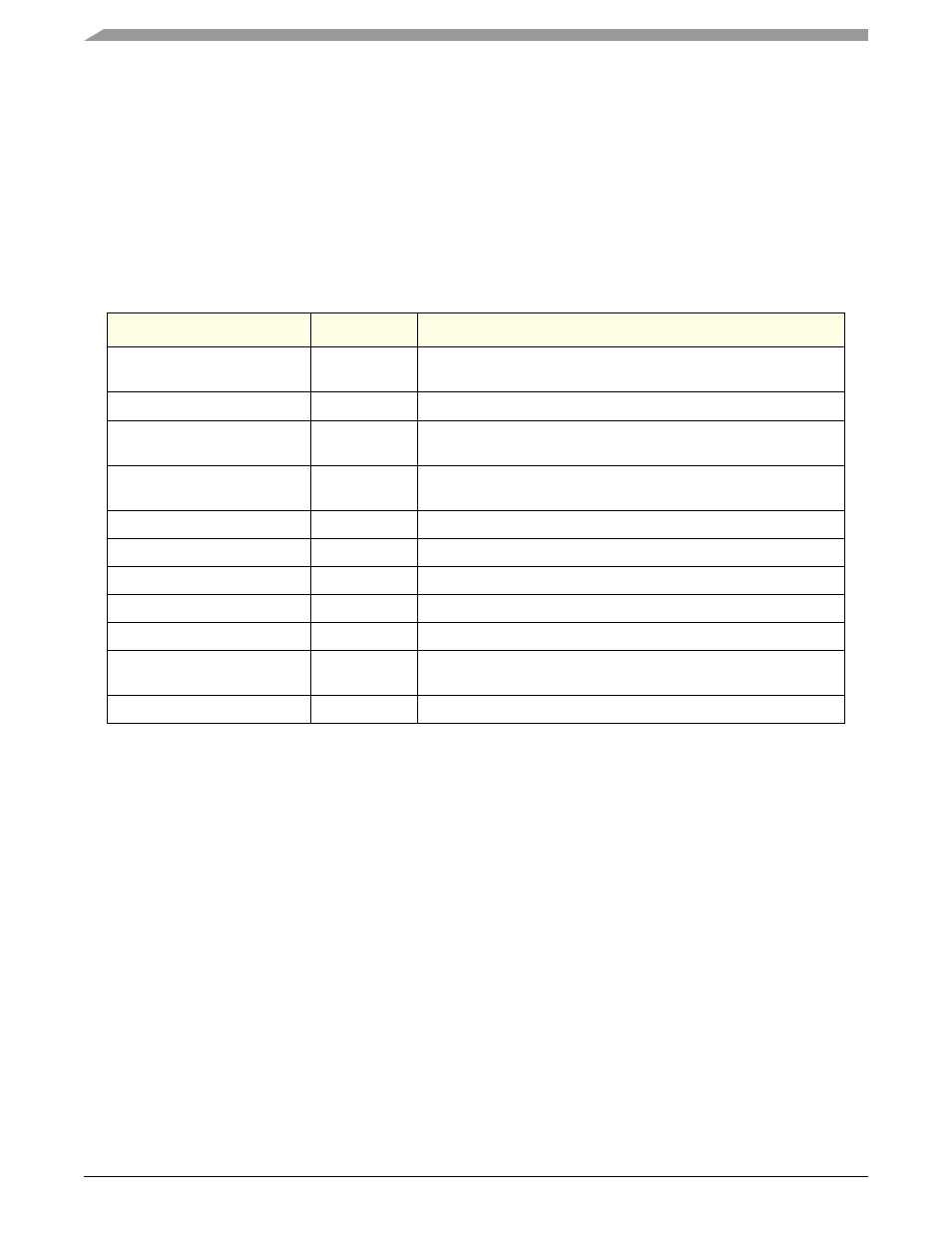

Table 15-80. 32-Bit “Soft Modem“Master Mode

Register

Value

Setting

0x0A

Disable the Tx and Rx part for configuration if the PSC was enabled

by the work before.

0x3FA00000

Select the 32bit Codec mode, lsb first, DTS1 = 1, master mode

cdm_psc2_bitclk_config

0x800F

divide the

f

system

clock frequency from 528 to 33MHz Mclk, see

Section 5.5.12, PSC2 Mclock Config Register—MBAR + 0x022C

cdm_clock_enable_register

0x00000040

Section 5.5.6, CDM Clock Enable Register—MBAR +

0x22830000

select the BitClk and FrameSync frequency

0x02

select the FrameSync width

0x000C

set the RFALARM level to 0x00C

TFALARM

0x0010

set the TFALARM level to 0x010

0x0100

enable TxRDY interrupt

Port_Config

0x00000070

Select the Pin-Muxing for PSC2 Codec mode, Mclk output enabled,

see

Chapter 2, Signal Descriptions

0x05

Enable Tx and Rx