Freescale Semiconductor MPC5200B User Manual

Page 458

BestComm DMA Registers—MBAR+0x1200

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

13-25

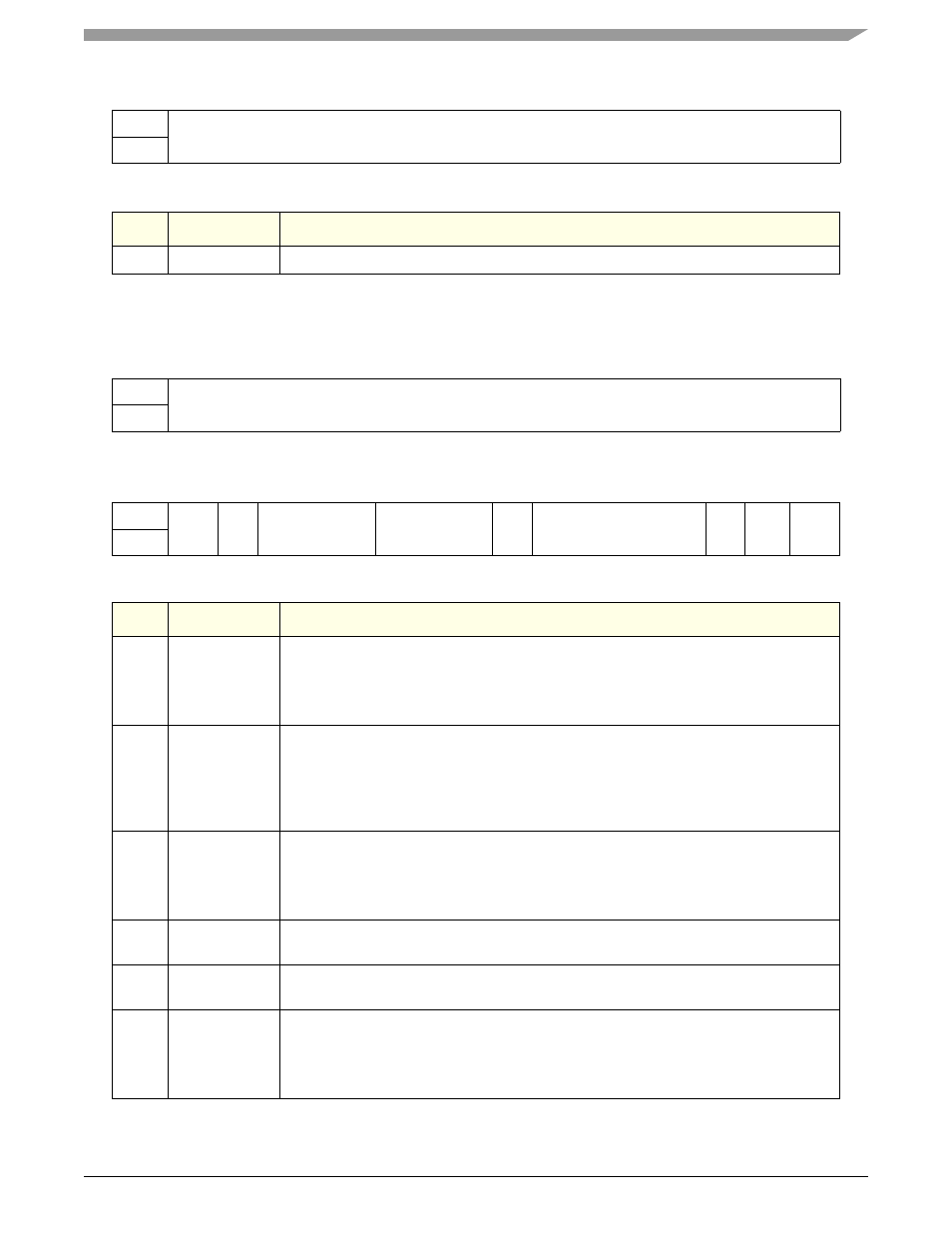

13.15.31 SDMA Debug Module Control Register—MBAR + 0x1278

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Value2

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

0:31

Value2

Debug Module Comparator 2 Value.

Table 13-32. SDMA Debug Module Control Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Block Tasks

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

AA

B

Comparator Type 1

Comparator Type 2

and/

or

EU breakpoints

E

I

B

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Name

Description

0:15

Block Tasks

Specify for each of tasks 15-0, whether to block that task with detection of a breakpoint (bit

0 halts TASK 15, bit 1 halts TASK 14, etc)

0 Do not block task

1 Block the task

16

AA

AutoArm—specifies whether or not the triggered bit dbgStatusReg[16] will be

automatically reset to 0 following the saving of context for a breakpoint. This bit is set to 0

at reset.

0 Triggered bit will not be automatically reset

1 Triggered bit will be automatically reset

17

B

Breakpoint—This bit specifies whether or not to take a breakpoint. This bit is set to 0 at

reset.

0 Disable breakpoints

1 Enable breakpoints

18:20

Comparator

Type 1

Comparator 1 type—These bits specify the type of data that has been loaded into

comparator 1; refer to

for the bit encoding.

21:23

Comparators

Type 2

Comparator 2 type—These bits specify the type of data that has been loaded into

comparator 2; refer to

for the bit encoding.

24

and / or

AND/OR—This specifies what type of operation is to be used with the comparators. This

bit is set to 0 at reset.

0 Indicates an OR’ing of the comparators

1 Indicates an AND’ing of the comparators