2 usb hc frame remaining register-mbar + 0x1038, 3 usb hc frame number register-mbar + 0x103c, Usb hc frame remaining register—mbar + 0x1038 -17 – Freescale Semiconductor MPC5200B User Manual

Page 420: Usb hc frame number register—mbar + 0x103c -17, Usb hc frame remaining register -17, Usb hc frame number register -17, Usb hc frame remaining register, Usb hc frame number register

Host Control (HC) Operational Registers

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

12-17

12.4.4.2

USB HC Frame Remaining Register—MBAR + 0x1038

This register is a 14-bit count-down counter containing the remaining current Frame bit-time.

12.4.4.3

USB HC Frame Number Register—MBAR + 0x103C

The HC Frame Number register is a 16-bit counter. It provides a timing reference among events happening in the HC and HCD. The HC driver

may use the 16-bit value specified in this register and generate a 32-bit frame number without requiring frequent access to the register.

Bits

Name

Description

0

FIT

FrameIntervalToggle—HCD toggles this bit when it loads a new value to the frame interval.

1:15

FSMPS

FSLargestDataPacket—specifies a value that is loaded into the largest data packet counter at

the beginning of each frame. The counter value represents the largest amount of data in bits

that the HC can send or received in a single transaction at any given time without causing

scheduling overrun. HCD calculates this field value.

16:17

—

Reserved

18:31

FI

FrameInterval—specifies the bit-time interval between two consecutive SOFs. Nominally, this

value is set to 11,999. HCD should store the field’s current value before resetting HC. Setting

the HcCommandStatus HostControllerReset field causes the HC to reset this field to its

nominal value. HCD may choose to restore the stored value when the reset sequence

completes.

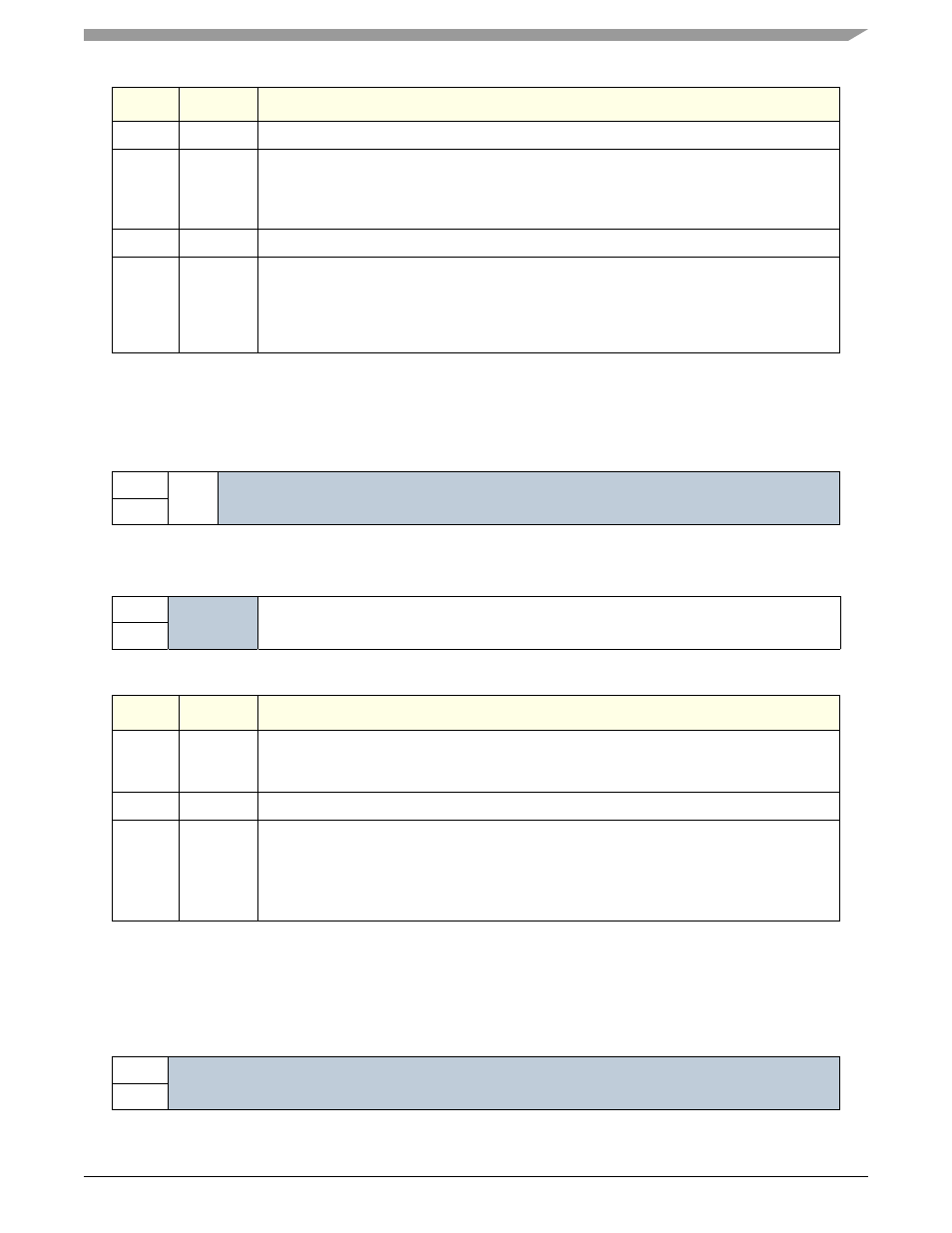

Table 12-15. USB HC Frame Remaining Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

FRT

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

FR

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0

FRT

FrameRemainingToggle—bit is loaded from the HcFmInterval FrameIntervalToggle field

when FrameRemaining reaches 0. HCD uses this bit for synchronization between

FrameInterval and FrameRemaining.

1:17

—

Reserved

18:31

FR

FrameRemaining—is a counter that is decremented at each bit-time. When it reaches 0, it is

reset by loading the FrameInterval value specified in HcFmInterval at the next bit-time

boundary.

When entering the USBOPERATIONAL state, HC reloads the content with the HcFmInterval

Frame Interval and uses the updated value from the next SOF.

Table 12-16. USB HC Frame Number Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0