3 ata drive data register-mbar + 0x3a60, Ata drive alternate status register, Ata drive data register – Freescale Semiconductor MPC5200B User Manual

Page 378

ATA Register Interface

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

11-13

11.3.3.2

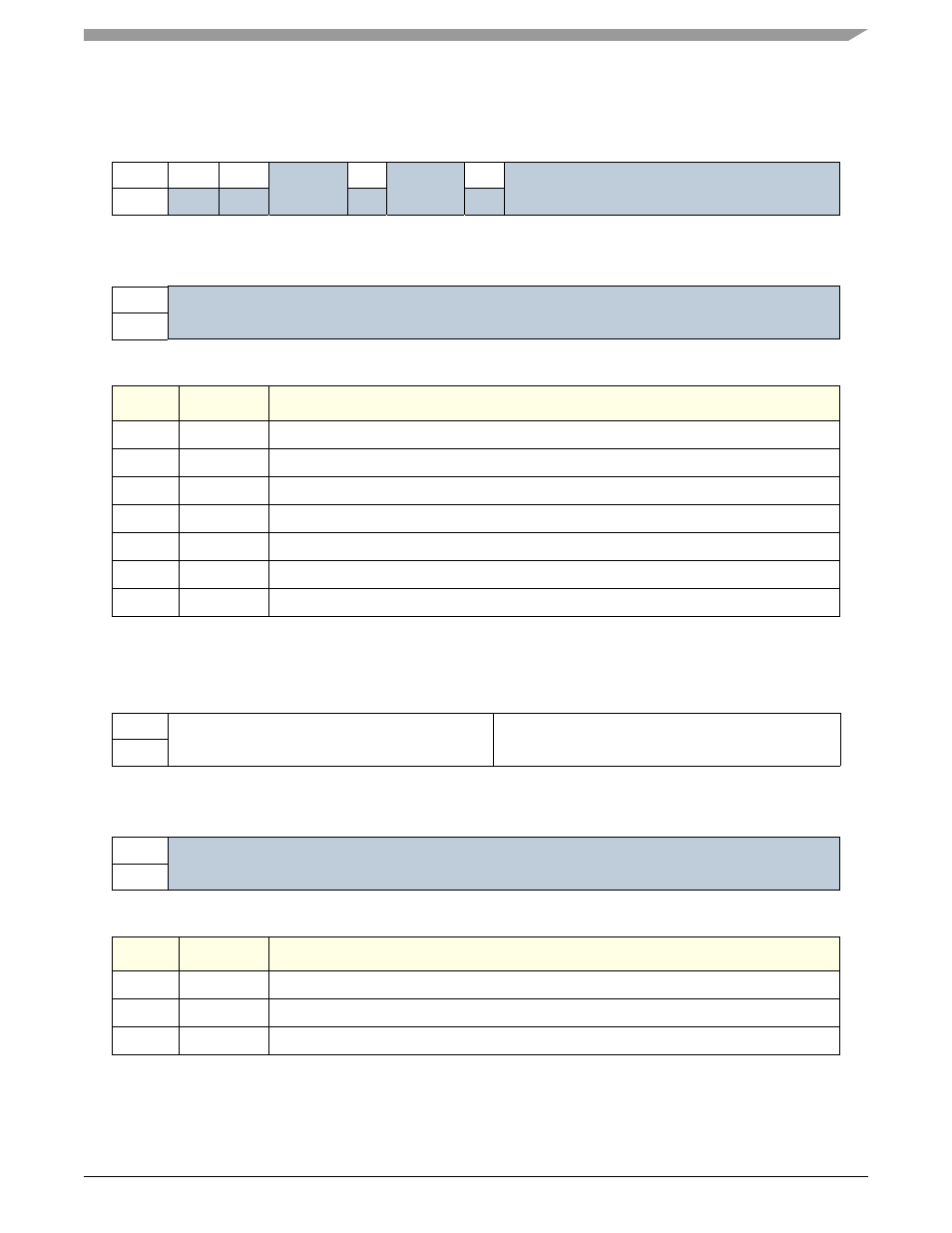

ATA Drive Alternate Status Register—MBAR + 0x3A5C

11.3.3.3

ATA Drive Data Register—MBAR + 0x3A60

Table 11-20. ATA Drive Alternate Status Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

BSY

DRDY

Reserved

DRQ

Rsvd

ERR

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0

BSY

Drive Busy—Transactions internal to drive are in progress. Host must wait.

1

DRDY

Drive Ready

2:3

—

Reserved

4

DRQ

Set to 1 indicates drive is ready to transfer a word of data.

5:6

—

Reserved

7

ERR

Indicates an error during the execution of the previous command.

8:31

—

Reserved

Table 11-21. ATA Drive Data Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Data H

Data L

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:7

Data H

Upper byte of drive data (read/write)

8:15

Data L

Lower byte of drive data (read/write)

16:31

—

Reserved