Freescale Semiconductor MPC5200B User Manual

Page 132

Reset Configuration

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

4-5

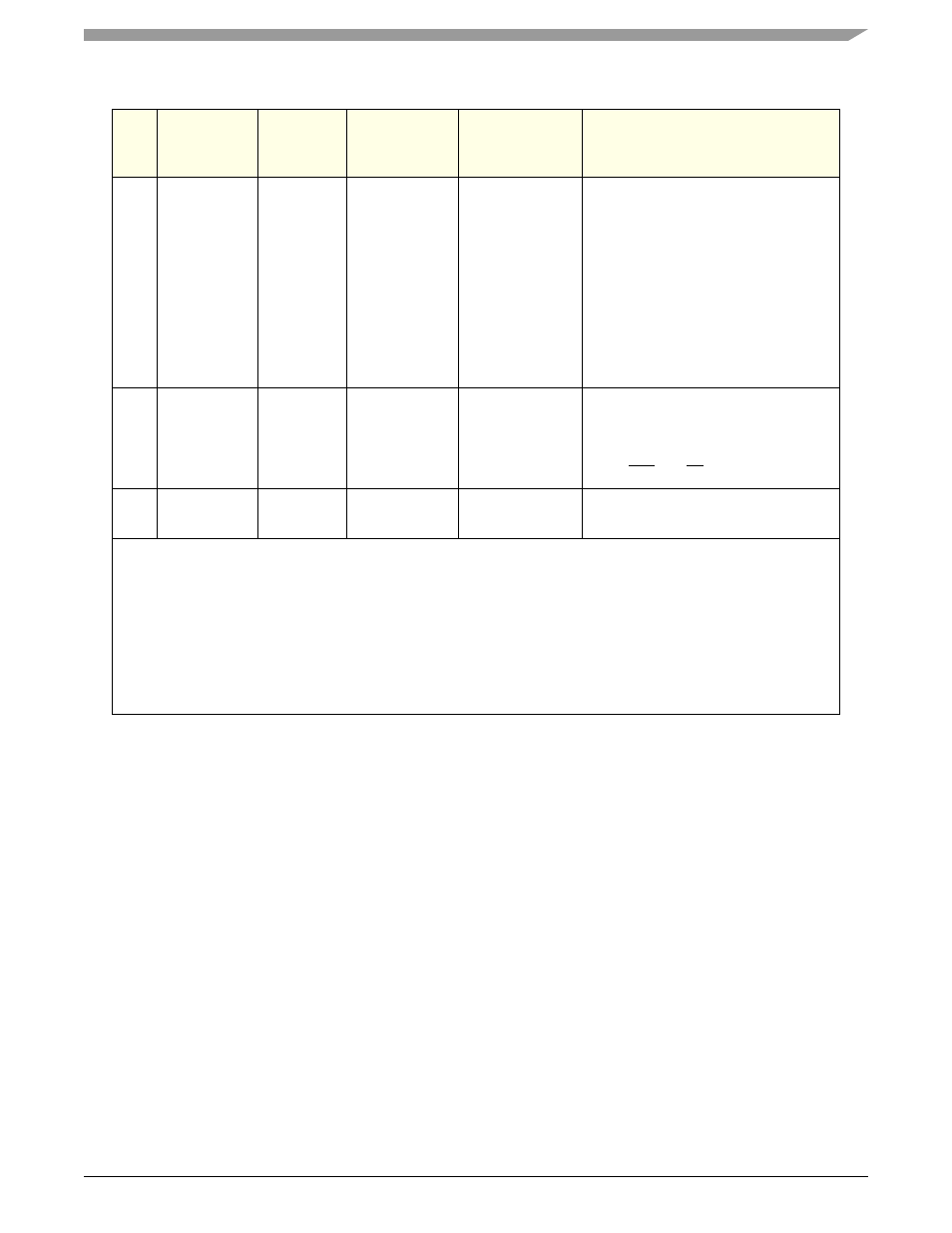

L03

RST_CFG13

ETH5

PORCFG[18]

boot_rom_size

For non-muxed boot ROMs:

2,3

bit=0:8bit boot ROM data bus, 24bit

max boot ROM address bus

bit=1:16bit boot ROM data bus, 16bit

boot ROM address bus

For muxed boot ROMs:

boot ROM address is max 25 significant

bits during address tenure.

bit=0:16bit ROM data bus

bit=1:32bit ROM data bus

N02

RST_CFG14

ETH6

PORCFG[17]

boot_rom_type

bit=0:non-muxed boot ROM bus,

single tenure transfer.

1

bit=1:muxed boot ROM bus, with

address and data tenures,

ALE and TS active.

1

K02

RST_CFG15

ETH1

PORCFG[16]

large_flash_sel

bit=0:No Boot in Large Flash Mode

1

bit=1:Boot in Large Flash Mode

1,3,4

Note:

1.

If multipe settings are choosen the following priorities are valid:

1. large_flash_sel

2. boot_rom_mg

3. boot_rom_type

2.

The boot_rom_size configuration signal doesn’t influence the address and data bus width of the MOST Graphics boot

mode configuration. The maximum address bus width is fixed to 24 bit and the data bus width is fixed to 32 bit.

3.

The boot_rom_size configurationsignal doesn’t influence the address bus width of the Large Flash boot mode

configuration. The maximum address bus width is fixed to 26 bit.

4.

The PCI controller is disabled, if booting in Large Flash or MOST Graphics mode is selected.

Table 4-2. Reset Configuration Word Source Pins (continued)

Pkg

Ball

Reset

Config Pin

I/O Signal

Name

CDM Reset

Config

Register Bit

Config Signal

from CDM

Description