Ictl main interrupt status all register, 0x052c) – Freescale Semiconductor MPC5200B User Manual

Page 175

MPC5200B Users Guide, Rev. 1

7-16

Freescale Semiconductor

Interrupt Controller

7.2.4.11

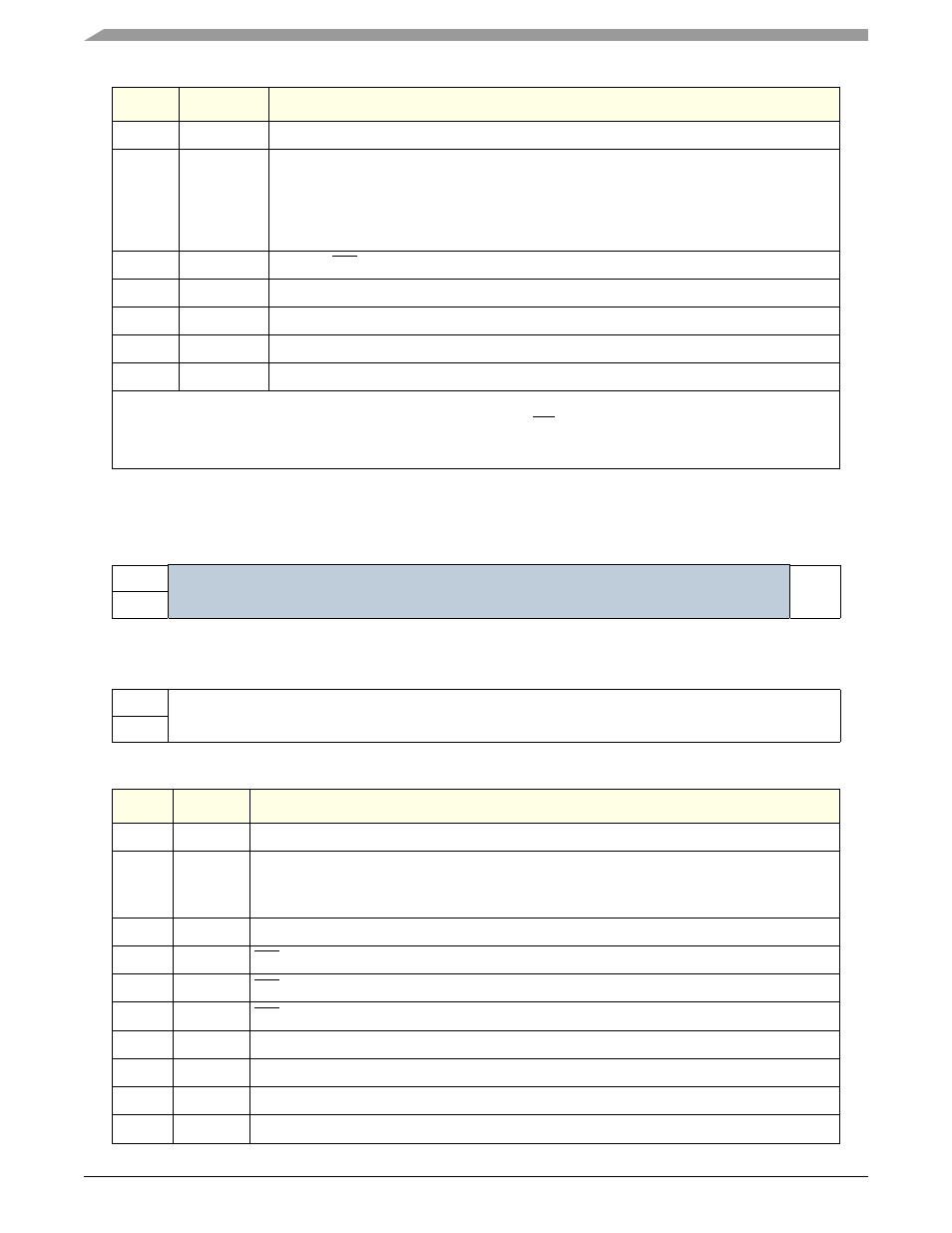

ICTL Main Interrupt Status All Register—MBAR + 0x052C

Bits

Name

Description

0:3

—

Reserved

—

CSa[x]

Critical Interrupt Status All—Indicates all pending interrupts, including the currently active

interrupt (if any). CSa is binary, showing each active interrupt input in its corresponding bit

position. See Note

1

.

Number in parenthesis indicates equivalent encoded value in CSe, ICTL PerStat, MainStat,

CritStat Encoded Register.

4

CSa0

indicates IRQ[0] interrupt

5

CSa1

Slice Timer 0 interrupt

6

CSa2

HI_int interrupt

7

CSa3

WakeUp from deep-sleep mode (CCS) interrupt

8:31

—

Reserved

Note:

1.

No direct mask register is defined for critical interrupts. However, IRQ[0] can be masked by the MEE bit in Reg4, in which

case CSa status does not occur. If only the EENA[0] bit in

ICTL External Enable and External Types

Register

is cleared, then CSa status occurs, but controller does not assert a e300 core interrupt.

Table 7-14. ICTL Main Interrupt Status All Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Reserved

MSa

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

MSa

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:14

—

Reserved

—

MSa[x]

Main Interrupt Status All. Indicates all pending interrupts. Is binary, showing each active

interrupt in its corresponding bit position. See Note

1

.

Number in parenthesis indicates equivalent encoded value in MSe, Reg9.

15

MSa0

Slice_Timer 1 (SMI interrupt only)

16

MSa1

IRQ[1] input pin

17

MSa2

IRQ[2] input pin

18

MSa3

IRQ[3] input pin

19

MSa4

LO_int (some Peripheral source)

20

MSa5

RTC_periodic interrupt

21

MSa6

RTC_stopwatch interrupt

22

MSa7

GPIO std interrupt