2 bestcomm write, 3 ata register interface, 1 ata host registers-mbar + 0x3a00 – Freescale Semiconductor MPC5200B User Manual

Page 367: 1 ata host configuration register-mbar + 0x3a00, Section 11.3.1, Section 11.3, ata register interface, Includes, Section 11.3.1, ata host registers—mbar + 0x3a00

MPC5200B Users Guide, Rev. 1

11-2

Freescale Semiconductor

ATA Register Interface

4.

As FIFO fills, BestComm is interrupted and moves data from FIFO to an internal destination.

11.2.2

BestComm Write

1.

microprocessor sets up descriptors in BestComm RAM and initiates a transfer.

2.

BestComm hits on an ATA command FIFO space and writes a command (ATA drive register address, transfer size) into FIFO.

3.

BestComm reads data from internal source and puts data in FIFO

4.

ATA Controller transfers data from FIFO and writes to drive.

NOTE

Any DMA transfer, where source and destination are both on the local bus, requires internal

BestComm SRAM buffering.

11.3

ATA Register Interface

The IPBI module contains all software-programmable ATA Controller registers and the IPB glue logic needed to read and write these registers.

The IPBI registers are listed below. Unless otherwise noted, each register is written and read from the same address.

11.3.1

ATA Host Registers—MBAR + 0x3A00

ATA is controlled by 10 32-bit registers. These registers are located at an offset from MBAR of 0x3A00. Register addresses are relative to

this offset. Therefore, the actual register address is:

MBAR + 0x3A00 + register address

Hyperlinks to the ATA Host registers are provided below:

11.3.1.1

ATA Host Configuration Register—MBAR + 0x3A00

•

ATA Host Configuration Register

(0x3A00)

•

ATA Ultra DMA Timing 1 Register

(0x3A18)

•

(0x3A04)

•

ATA Ultra DMA Timing 2 Register

(0x3A1C)

•

(0x3A08)

•

ATA Ultra DMA Timing 3 Register

(0x3A20)

•

(0x3A0C)

•

ATA Ultra DMA Timing 4 Register

(0x3A24)

•

ATA Multiword DMA Timing 1 Register

•

ATA Ultra DMA Timing 5 Register

(0x3A28)

•

ATA Multiword DMA Timing 2 Register

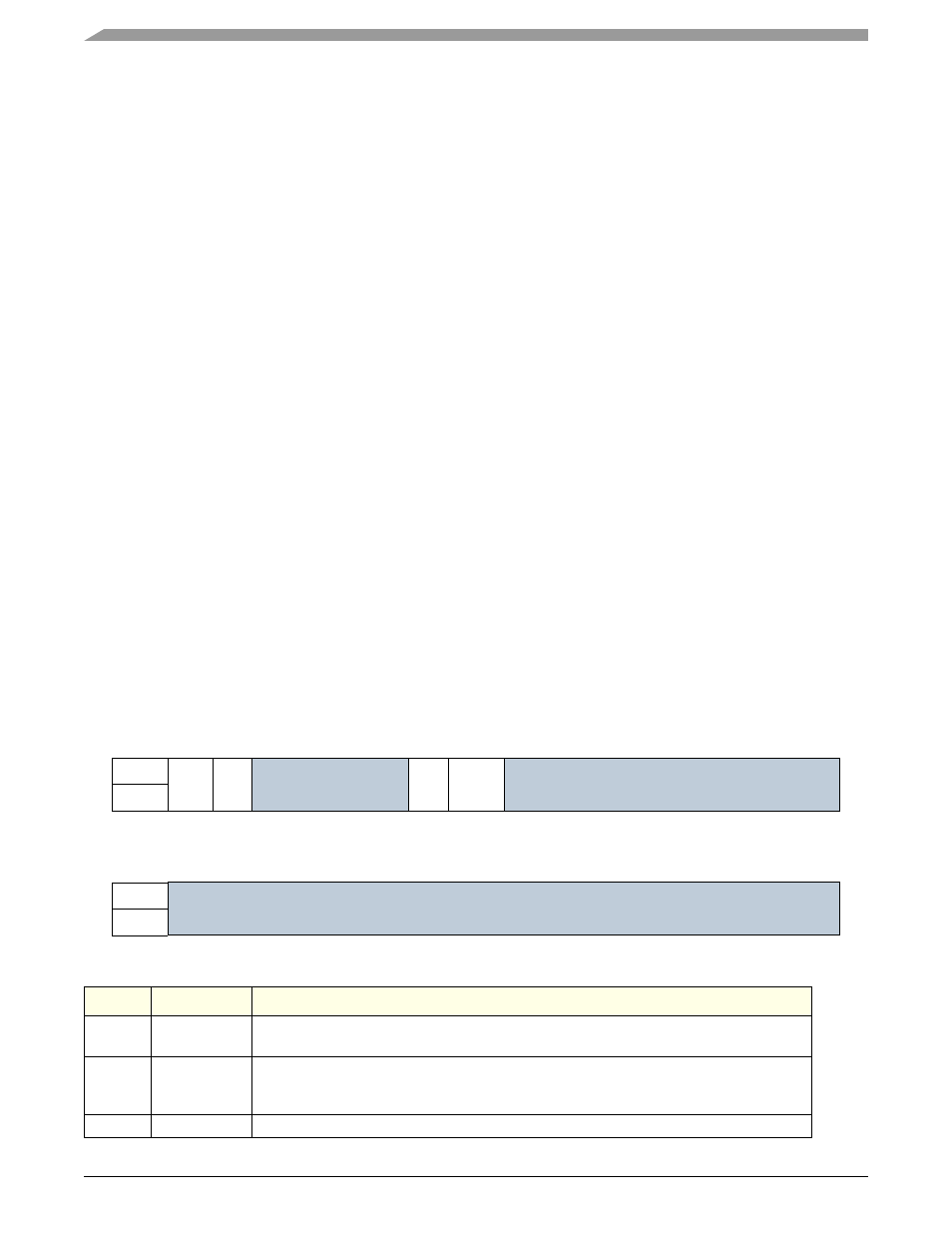

Table 11-1. ATA Host Configuration Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

SMR

FR

Reserved

IE

IORDY

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0

SMR

State Machine Reset—bit resets ATA state machine to IDLE state for PIO, DMA and UDMA

read/write.

1

FR

FIFO Reset—bit can be used to reset FIFO when bit 0 of this register is set to reset the

ATA state machine. During normal ATA transaction, FIFO can be reset by setting ATA Drive

Command Register FR bit (see

2:5

—

Reserved