11 interrupt mask register (0x14)-imr, Interrupt mask register (0x14)—imr -18, Interrupt mask register (0x14)—imr – Freescale Semiconductor MPC5200B User Manual

Page 531: Esponding, Corresponding

MPC5200B Users Guide, Rev. 1

15-20

Freescale Semiconductor

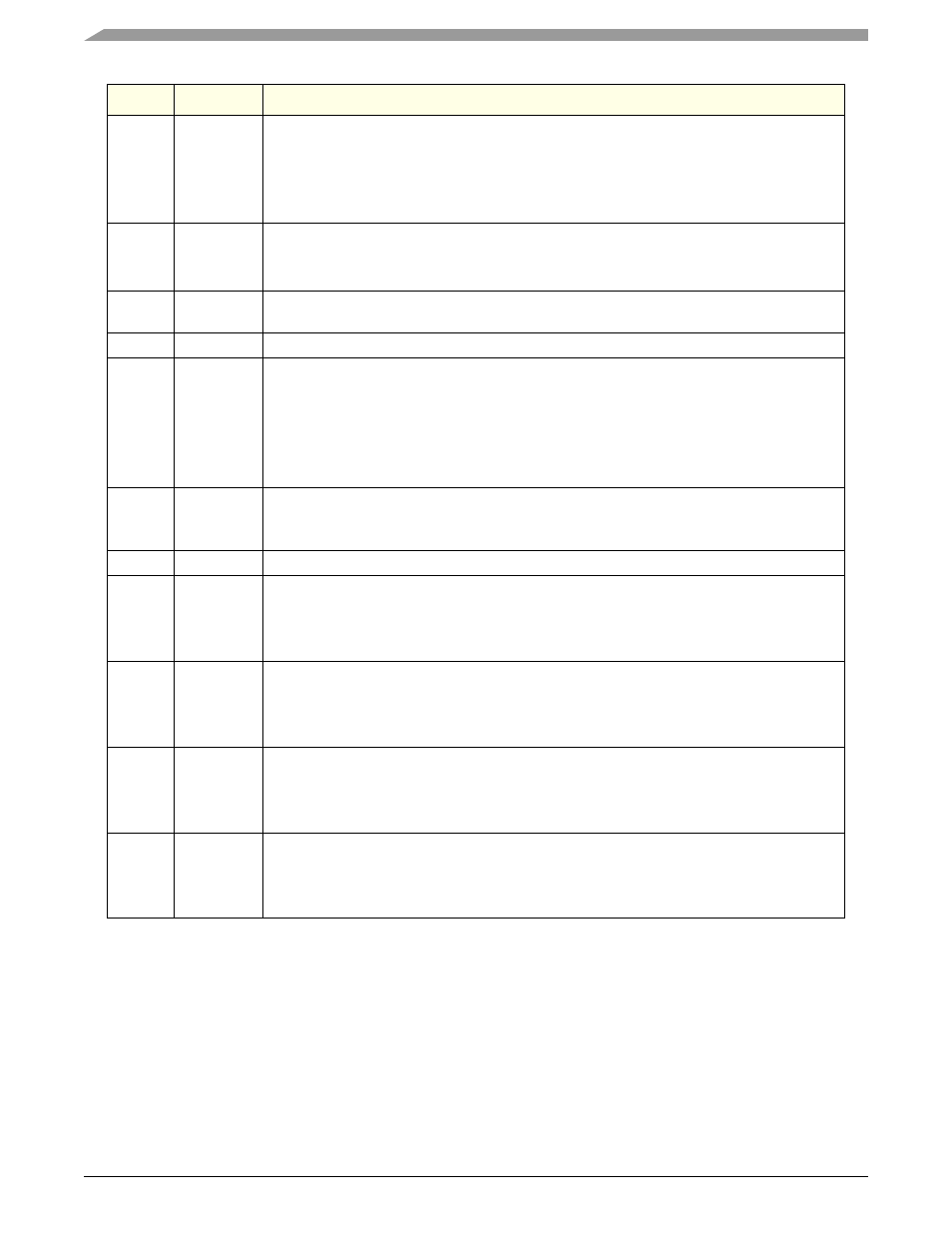

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

15.2.11

Interrupt Mask Register (0x14)

—

IMR

The write-only IMR register selects corresponding bits in the

•

If one

bit is set and the corresponding IMR bit is also set, the internal interrupt output is asserted.

•

If the corresponding bit in IMR is 0, the state of the

bit has no effect on the interrupt output. The IMR does not mask reading

the

4

TxEMP/

URERR

UART / SIR—TxEMP

This bit is identical to the URERR bit in the

register.

other Modes—Underrun Error

This bit is identical to the URERR bit in the

register. To clear this interrupt use the reset

error status command in the

register.

5

DB

UART / SIR—Delta Break

Receiver detect an Delta Break state.

other Modes—Reserved

6

RxRDY

FFULL

Rx FIFO over threshold. If

[1]=1, then this bit is identical to the FFULL bit in the

register. If

[1]=0, then this bit is identical to the RxRDY bit in the

register.

7

TxRDY

Transmitter ready - identical to the TxRDY bit in the

register

8

DEOF

MIR / FIR—Detect End of Frame

0 = Rx did not receive an EOF after the last read

command.

1 = Rx received the EOF in the frame. In this case, the interrupt and request can be

asserted even if the Rx FIFO number is less than the threshold and

[1]=1.

To clear this interrupt use the reset error status command in the

register.

other Modes—Reserved

9

Error

Error

This bit is identical to the Error bit in the

register. To clear this interrupt use the reset

error status command in the

10:11

—

Reserved

12

CMD_SEND

Enhanced AC97 Mode—Command Send ready

This bit is identical to the CMD_SEND bit in the

register. To clear this interrupt use the

reset error status command in the

register.

other Modes—Reserved

13

DATA_OVR

Enhanced AC97 Mode—Receive Data Overwrite

This bit is identical to the DATA_OVR bit in the

register. To clear this interrupt use the

reset error status command in the

register.

other Modes—Reserved

14

DATA_VALID

Enhanced AC97 Mode—Received Status Data

This bit is identical to the DATA_VALID bit in the

register. To clear this interrupt use the

reset error status command in the

register.

other Modes—Reserved

15

UNEX_RX_

SLOT

Enhanced AC97 Mode—Unexpected RX Slots detect

This bit is identical to the UNEX_RX_SLOT bit in the

register. To clear this interrupt use

the reset error status command in the

register.

other Modes—Reserved

Bit

Name

Description