Bdlc state vector register -7, Section 20.7.3.2, bdlc state vector, Register (dlcbsvr) - mbar + 0x1300 – Freescale Semiconductor MPC5200B User Manual

Page 686: Bdlc state vector register, Table 1-1. interrupt summary

Memory Map and Registers

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

20-7

1 = Stop BDLC internal clocks during CPU wait mode (BDLC_STOP)

0 = Run BDLC internal clocks during CPU wait mode (BDLC_WAIT)

20.7.3.2

BDLC State Vector Register (DLCBSVR) - MBAR + 0x1300

This register is provided to substantially decrease the CPU overhead associated with servicing interrupts while under operation of a MUX

protocol. It provides a index offset that is directly related to the BDLC module’s current state, which can be used with a user supplied jump

table to rapidly enter an interrupt service routine. This eliminates the need for the user to maintain a duplicate state machine in software.

READ: any time

WRITE: ignored

I[3:0]

—

Interrupt State Vector (Bits 5- 2)

These bits indicate the source of the interrupt request that is currently pending.

The state encoding of the interrupt sources mean that only one interrupt source is dealt with at a time. Once the highest priority interrupt source

is dealt with, if another interrupt event of a lower priority has also occurred, the value corresponding to that interrupt source appears in the

BDLC State Vector Register. This continues until all BDLC interrupt sources have been dealt with and all bits in the BDLC State Vector

Register are cleared.

•

Wakeup

The BDLC has two different power-conserving modes, stop and wait. Wakeup from these modes is described below.

•

Wakeup from BDLC Wait with CPU in Wait

If the CPU executes a WAIT instruction and the BDLC enters the BDLC wait mode, the clocks to the BDLC as well as the clocks

in the MCU continue to run. The message which generates a Wake-up interrupt of the BDLC and the CPU will be received correctly.

•

Wakeup from BDLC Stop with CPU in Wait

If the CPU executes a WAIT instruction and the BDLC enters the BDLC stop mode, the clocks to the BDLC are turned off, but the

clocks in the MCU continue to run. The message which generates a Wake-up interrupt of the BDLC and the CPU will be received

correctly. To ensure this, the EOF following the last message appearing on the bus must be received; otherwise, the message will

not be received correctly.

•

Wakeup from BDLC Stop with CPU in Stop

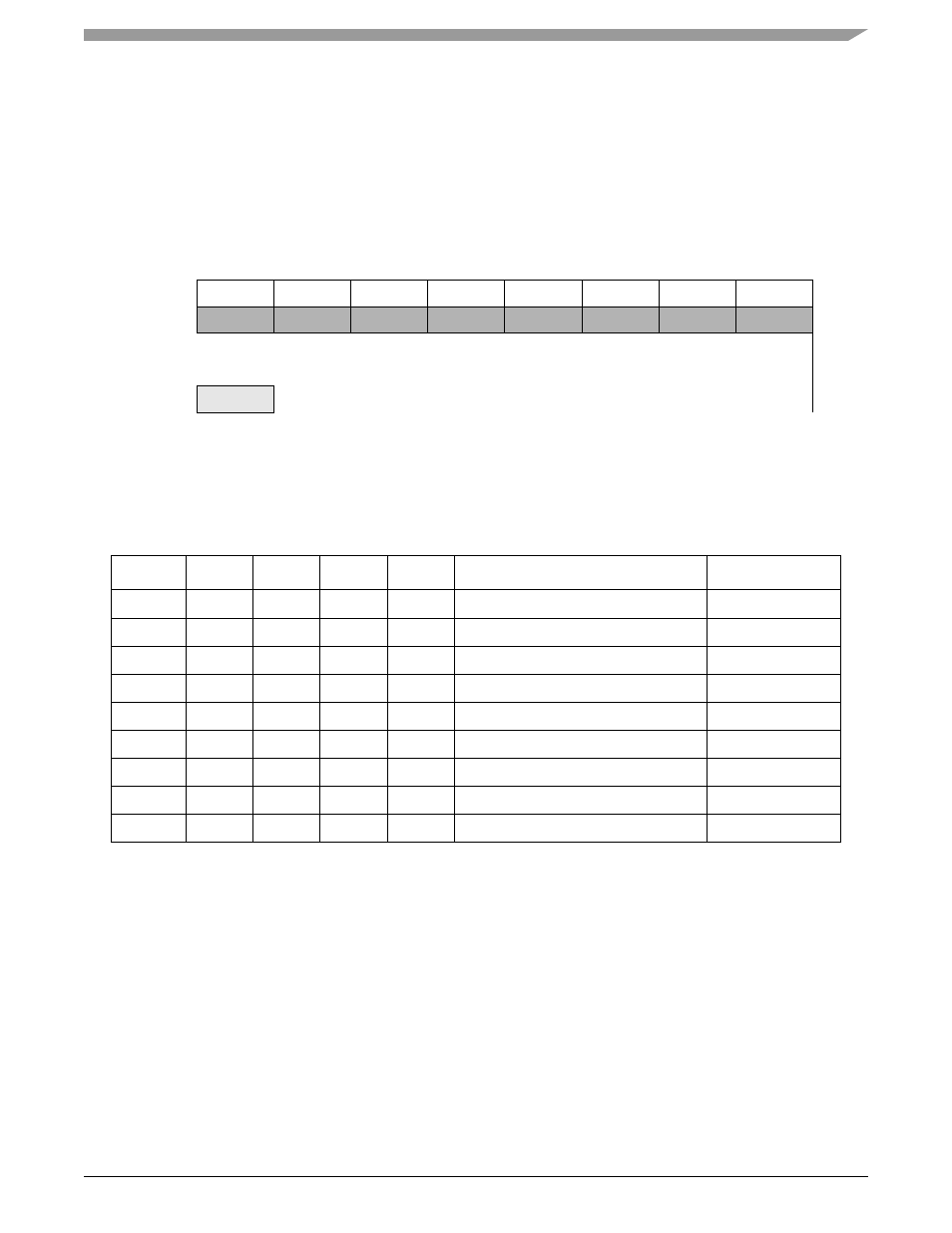

Table 20-3.

BDLC State Vector Register

msb 0

1

2

3

4

5

6

7 lsb

R

0

0

I3

I2

I1

I0

0

0

W

RESET:

0

0

0

0

0

0

0

0

= Unimplemented or Reserved

Table 1-1. Interrupt Summary

BSVR

I3

I2

I1

I0

Interrupt Source

Priority

$00

0

0

0

0

No Interrupts Pending

0 (Lowest)

$04

0

0

0

1

Received EOF

1

$08

0

0

1

0

Received IFR byte

2

$0C

0

0

1

1

Rx data register full

3

$10

0

1

0

0

Tx data register empty

4

$14

0

1

0

1

Loss of arbitration

5

$18

0

1

1

0

CRC error

6

$1C

0

1

1

1

Symbol invalid or out of range

7

$20

1

0

0

0

Wakeup

8 (Highest)