Freescale Semiconductor MPC5200B User Manual

Page 648

Memory Map / Register Definition

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

19-9

19.5.6

MSCAN Bus Timing Register 1 (CANBTR1)—MBAR + 0x0905 / 0x985

The MSCAN Bus Timing Register 1 provides for various bus timing control of the MSCAN module.

Read: Anytime

Write: Anytime in Initialization Mode (INITRQ = 1 and INITAK = 1)

Read: Anytime

Write: Anytime in Initialization Mode (INITRQ = 1 and INITAK = 1)

Bit-time, as shown below, is determined by:

•

oscillator frequency

•

baud rate prescaler

•

number of time quanta (Tq) clock cycles per bit

and

give time segment values.

1

1

1

1

1

0

63

1

1

1

1

1

1

64

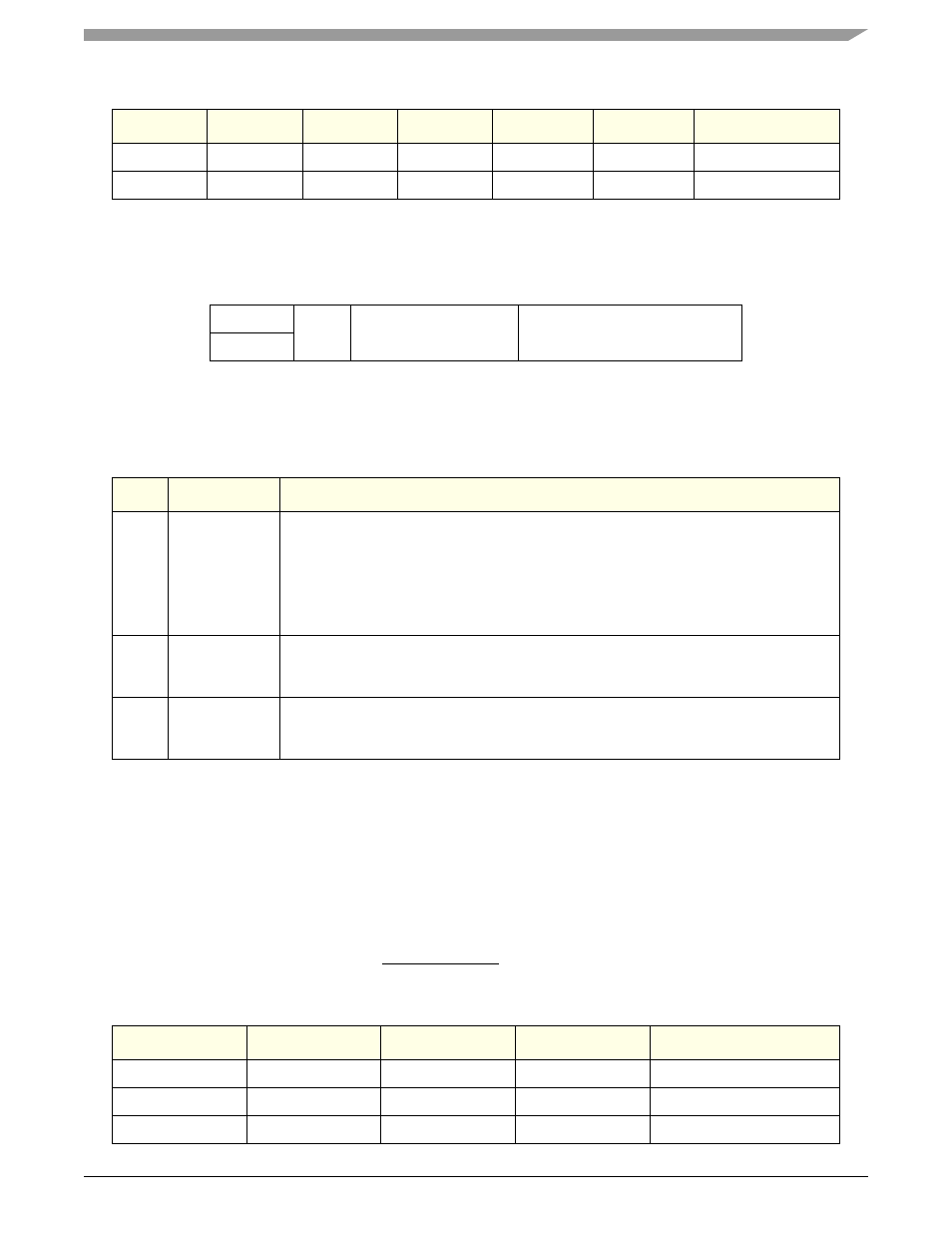

Table 19-7. MSCAN Bus Timing Register 1

msb 0

1

2

3

4

5

6

7 lsb

R

SA

MP

TSEG[22:20]

TSEG[13:10]

W

RESET:

0

0

0

0

0

0

0

0

Bit

Name

Description

0

SAMP

Sampling—bit determines number of serial bus samples taken per bit-time. If set, three

samples per bit are taken; the regular one (sample point) and two preceding samples using

a majority rule. For higher bit-rates, it is recommended that SAMP be cleared, which

means only one sample is taken per bit.

0 = One sample per bit

1 = Three samples per bit

1:3

TSEG[22:20]

Time Segment 2—time segments within the bit-time, fix the number of clock cycles per

bit-time and the location of the sample point. Time segment 2 (TSEG2) values are

programmable as shown in

4:7

TSEG[13:10]

Time Segment 1—time segments within the bit-time, fix the number of clock cycles per

bit-time and the location of the sample point. Time segment 1 (TSEG1) values are

programmable as shown in

Table 19-8. Time Segment 1 Values

TSEG13

TSEG12

TSEG11

TSEG10

Time segment 1

0

0

0

0

1 Tq clock cycle (a)

0

0

0

1

2 Tq clock cycles (1)

0

0

1

0

3 Tq clock cycles (1)

Table 19-6. Baud Rate Prescaler (continued)

BRP5

BRP4

BRP3

BRP2

BRP1

BRP0

Prescaler Value (P)

Bit Time = (Prescaler value)

(Number of Time Quanta)

f

CANCLK

•