20 output port 1 bit set (0x38)-op1, 21 output port 0 bit set (0x3c)-op0, Output port 1 bit set (0x38)—op1 -24 – Freescale Semiconductor MPC5200B User Manual

Page 540: Output port 0 bit set (0x3c)—op0 -24, Output port 1 bit set (0x38)—op1, Output port 0 bit set (0x3c)—op0

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

MPC5200B Users Guide, Rev. 1

Freescale Semiconductor

15-29

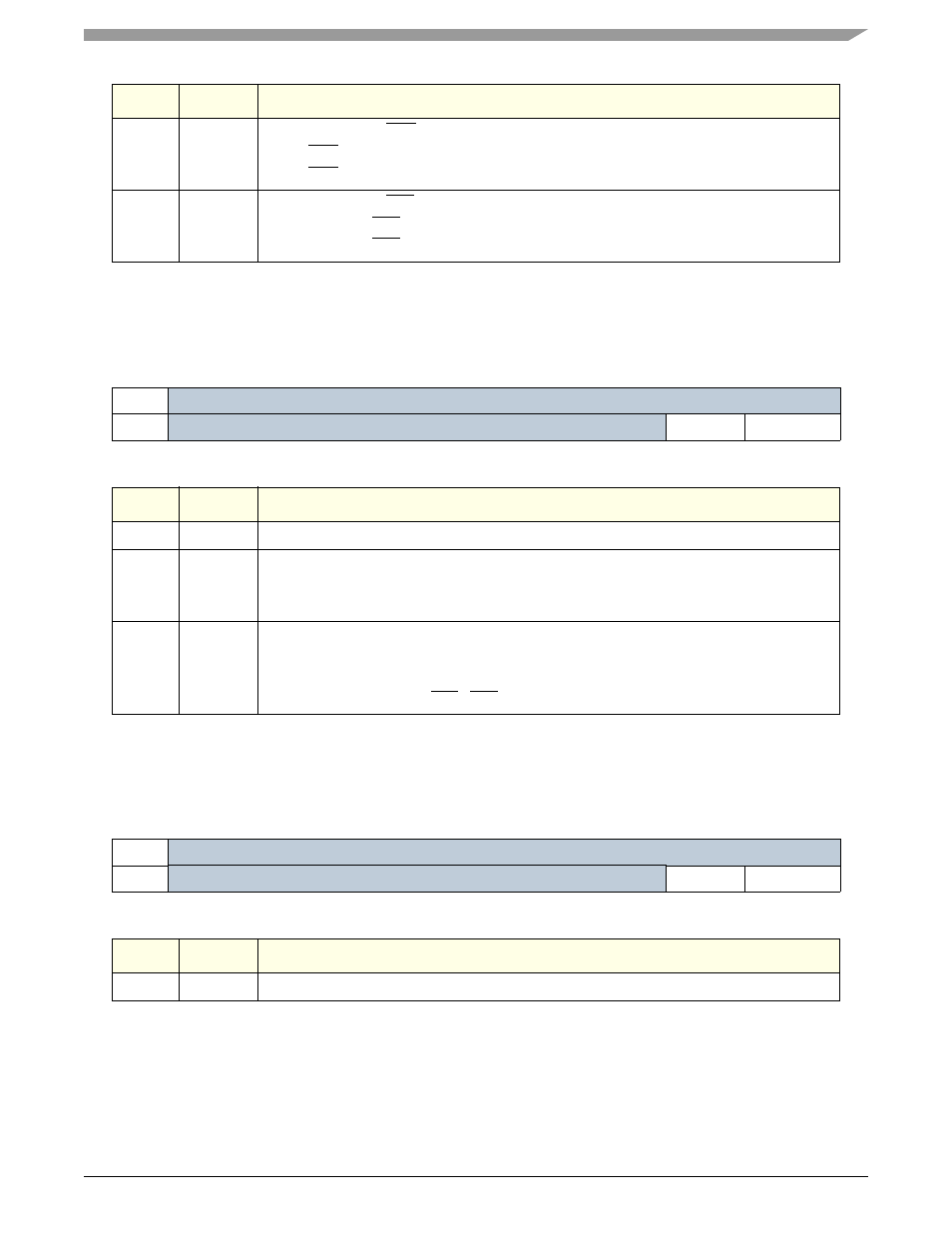

15.2.20

Output Port 1 Bit Set (0x38)

—

OP1

This is a write-only register. Output ports are asserted by writing to this register.

15.2.21

Output Port 0 Bit Set (0x3C)

—

OP0

This is a write-only register. Output ports are negated by writing to this register.

6

DCD

Current state of the DCD input.

0 = DCD input is low.

1 = DCD input is high.

7

CTS

Current state of the CTS input

0 = Input port CTS is low.

1 = Input port CTS is high.

Table 15-42. Output Port 1 Bit Set Register (0x38) for all Modes

msb 0

1

2

3

4

5

6

7 lsb

R

Reserved

W

Reserved

RES

RTS

RESET:

0

0

0

0

0

0

0

0

Bit

Name

Description

0:5

—

Reserved

6

RES

Assert RES output.

0 = No operation

1 = Asserts output port RES, (RES becomes 0)

7

RTS

AC97—Reserved

other Modes—Assert RTS output.

0 = No operation

1 = Asserts output port RTS, (RTS becomes 0)

Table 15-43. Output Port 0 Bit Set Register (0x3C) for all Modes

msb 0

1

2

3

4

5

6

7 lsb

R

Reserved

W

Reserved

RES

RTS

RESET:

0

0

0

0

0

0

0

0

Bit

Name

Description

0:5

—

Reserved

Bit

Name

Description