12 counter timer upper register (0x18)-ctur, Counter timer upper register (0x18)—ctur -19, Counter timer upper register (0x18)—ctur – Freescale Semiconductor MPC5200B User Manual

Page 533: The csr, Ctur

MPC5200B Users Guide, Rev. 1

15-22

Freescale Semiconductor

PSC Registers—MBAR + 0x2000, 0x2200, 0x2400, 0x2600, 0x2800, 0x2C00

15.2.12

Counter Timer Upper Register (0x18)

—

CTUR

This write-only register holds the upper bytes of the preload value used by the timer to provide a given Baud rate. Reading from this register

shows the current value of the Baud rate generation counter.For a detailed description see the next section,

Section 15.2.13, Counter Timer

8

DEOF

MIR / FIR Detect End of Frame

0 = DEOF has no effect on the interrupt.

1 = Enable the interrupt for DEOF.

other Modes—Reserved

9

Error

Error

0 = Error bit in the

register has no effect on the interrupt.

1 = Enable the interrupt for Error

10:11

—

Reserved

12

CMD_SEND

Enhanced AC97 Mode—Command Send ready

0 = CMD_SEND bit in the

register has no effect on the interrupt.

1 = Enable the interrupt for CMD_SEND

other Modes—Reserved

13

DATA_OVR

Enhanced AC97 Mode—Receive Data Overwrite

register has no effect on the interrupt.

1 = Enable the interrupt for DATA_OVR

other Modes—Reserved

14

DATA_VALID

Enhanced AC97 Mode—Received Status Data

0 = DATA_VALID bit in the

register has no effect on the interrupt.

1 = Enable the interrupt for DATA_VALID

other Modes—Reserved

15

UNEX_RX_

SLOT

Enhanced AC97 Mode—Unexpected RX Slots detect

0 = UNEX_RX_SLOT bit in the

register has no effect on the interrupt.

1 = Enable the interrupt for UNEX_RX_SLOT

other Modes—Reserved

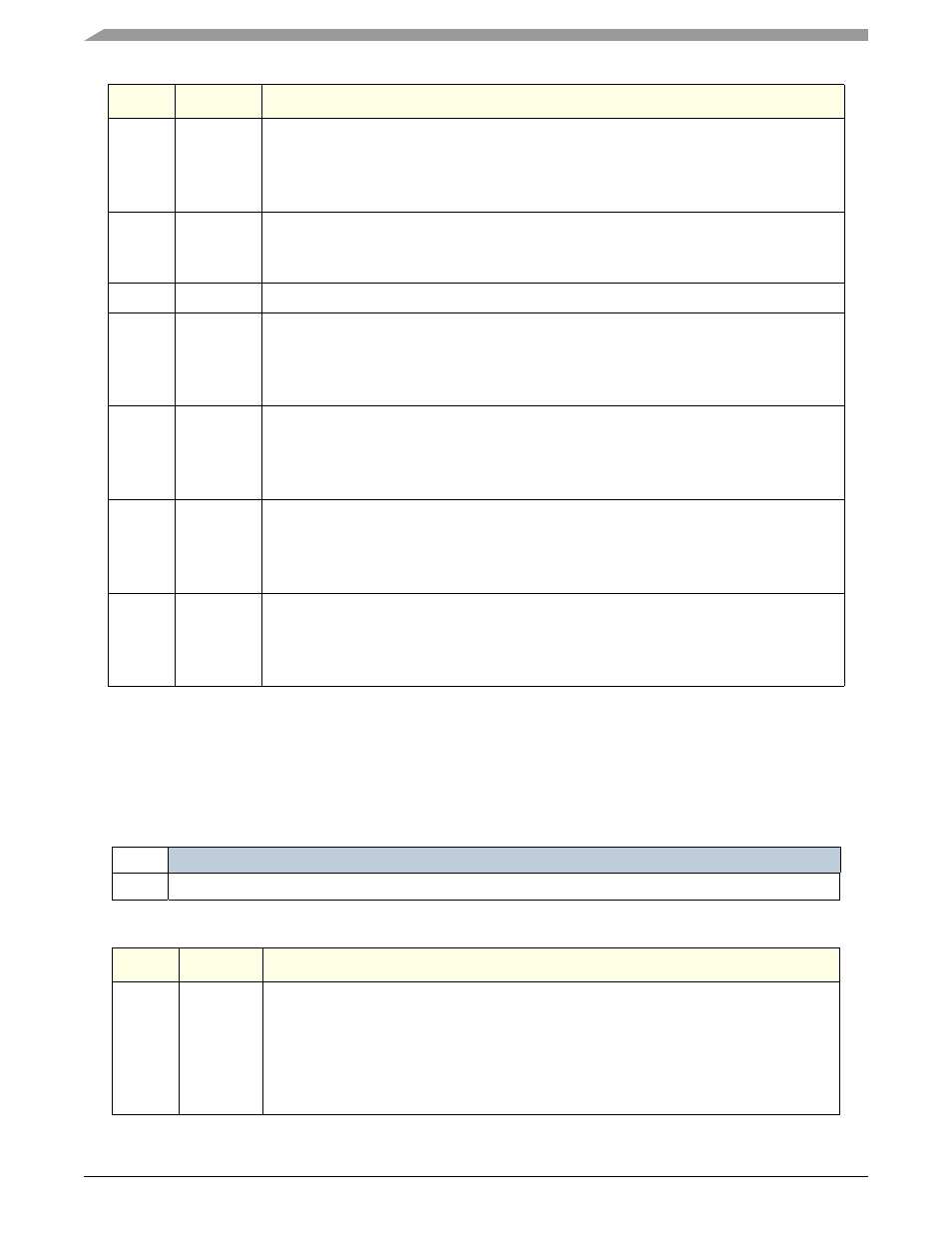

Table 15-30. Counter Timer Upper Register (0x18) for all Modes

msb 0

1

2

3

4

5

6

7 lsb

R

Reserved

W

CTUR[0:7]

RESET:

0

0

0

0

0

0

0

0

Bit

Name

Description

0:7

CTUR

Code—Frame Sync width, define the number of Bit clocks during the FrameSync signal is

active.

FrameSync Width = CTUR[0:7]+1

UART/ SIR/ SPI —Baud rate prescaler value.

See next section,

Section 15.2.13, Counter Timer Lower Register (0x1C)—CTLR

Other—Reserved

Bit

Name

Description