Table 5-5 – Freescale Semiconductor MPC5200B User Manual

Page 139

MPC5200B Users Guide, Rev. 1

5-6

Freescale Semiconductor

MPC5200B Clock Domains

gives the e300 Core APLL and operating frequency options compared to the xlb_clk reference input (shown in

selection of an e300 Core frequency is made at Power-On Reset (POR) via the reset configuration inputs. For more information see

Section 4.6, Reset Configuration.

Frequency ranges indicated in

represent possible ranges for the processor APLL. A variety of conditions may prevent the part from

actually performing at these frequency ranges. For data relating to actual performance, see the MPC5200B

Hardware Specification.

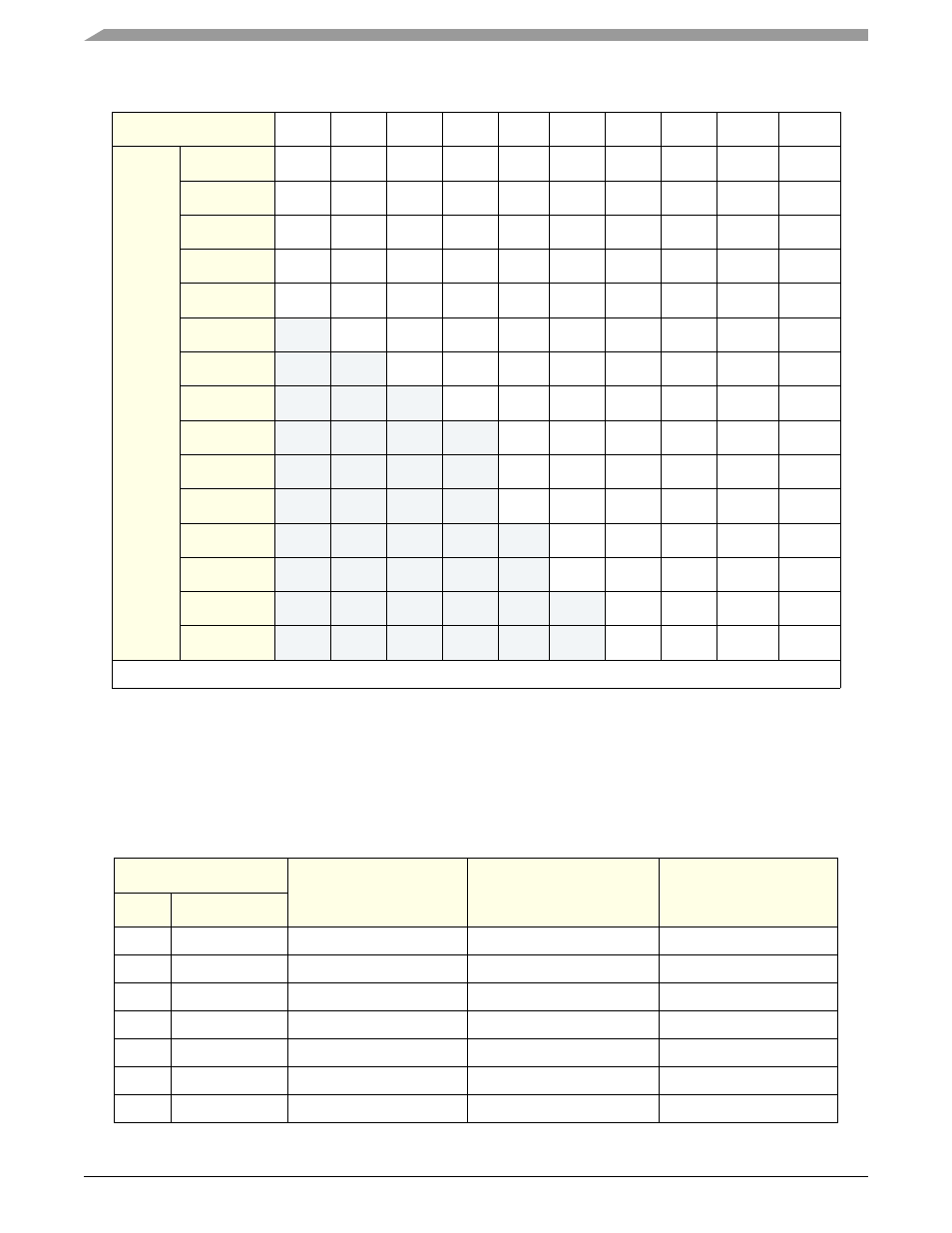

Table 5-5. e300 Core Frequencies vs. XLB Frequencies

XLB Clock (MHz)

132

108

99

81

66

54

49.5

40.5

33

27

e30

0 Cor

e

PLL Bus to Cor

e

Multiplier

a

a

See

, XLB to CORE clock ratio.

x1

—

—

—

—

—

—

—

—

—

—

x1.5

—

—

—

—

—

—

—

—

—

—

x2

264

216

198

162

132

108

99

81

66

54

x2.5

330

270

247.5

202.5

165

135

123.8

101.3

82.5

67.5

x3

396

324

297

243

198

162

148.4

121.5

99

81

x3.5

378

346.5

283.5

231

189

173.3

141.8

115.5

94.5

x4

396

324

264

216

198

162

132

108

x4.5

364.5

297

243

222.8

182.3

148.5

121.5

x5

330

270

247.5

202.5

165

135

x5.5

363

297

272.3

222.8

181.5

148.5

x6

396

324

297

243

198

162

x6.5

351

321.8

263.3

214.5

175.5

x7

378

346.5

283.5

231

189

x7.5

371.3

303.8

247.5

202.5

x8

396

324

264

216

Note: 1x and 1.5x multiply ratios are not available in this version of the MPC5200B.

Table 5-6. e300 Core APLL Configuration Options

ppc_pll_cfg

Bus:Core Ratio

(XLB : CORE CLOCK)

Core:VCO Ratio

(CORE CLOCK: f

VCOcore

)

Bus:VCO Ratio

(XLB : f

VCOcore)

hex

[0:1:2:3:4]

0x00

00000

—

—

—

0x01

00001

—

—

—

0x02

00010

—

—

—

0x04

00100

1:2

1:2

1:4

0x05

00101

1:2

1:4

1:8

0x06

00110

1:2.5

1:2

1:5

0x07

00111

1:4.5

1:2

1:9