8 ata drive cylinder low register-mbar + 0x3a70, 9 ata drive cylinder high register-mbar + 0x3a74, Ata drive cylinder low register (0x3a70) – Freescale Semiconductor MPC5200B User Manual

Page 381: Ata drive cylinder high register (0x3a74)

MPC5200B Users Guide, Rev. 1

11-16

Freescale Semiconductor

ATA Register Interface

11.3.3.8

ATA Drive Cylinder Low Register—MBAR + 0x3A70

11.3.3.9

ATA Drive Cylinder High Register—MBAR + 0x3A74

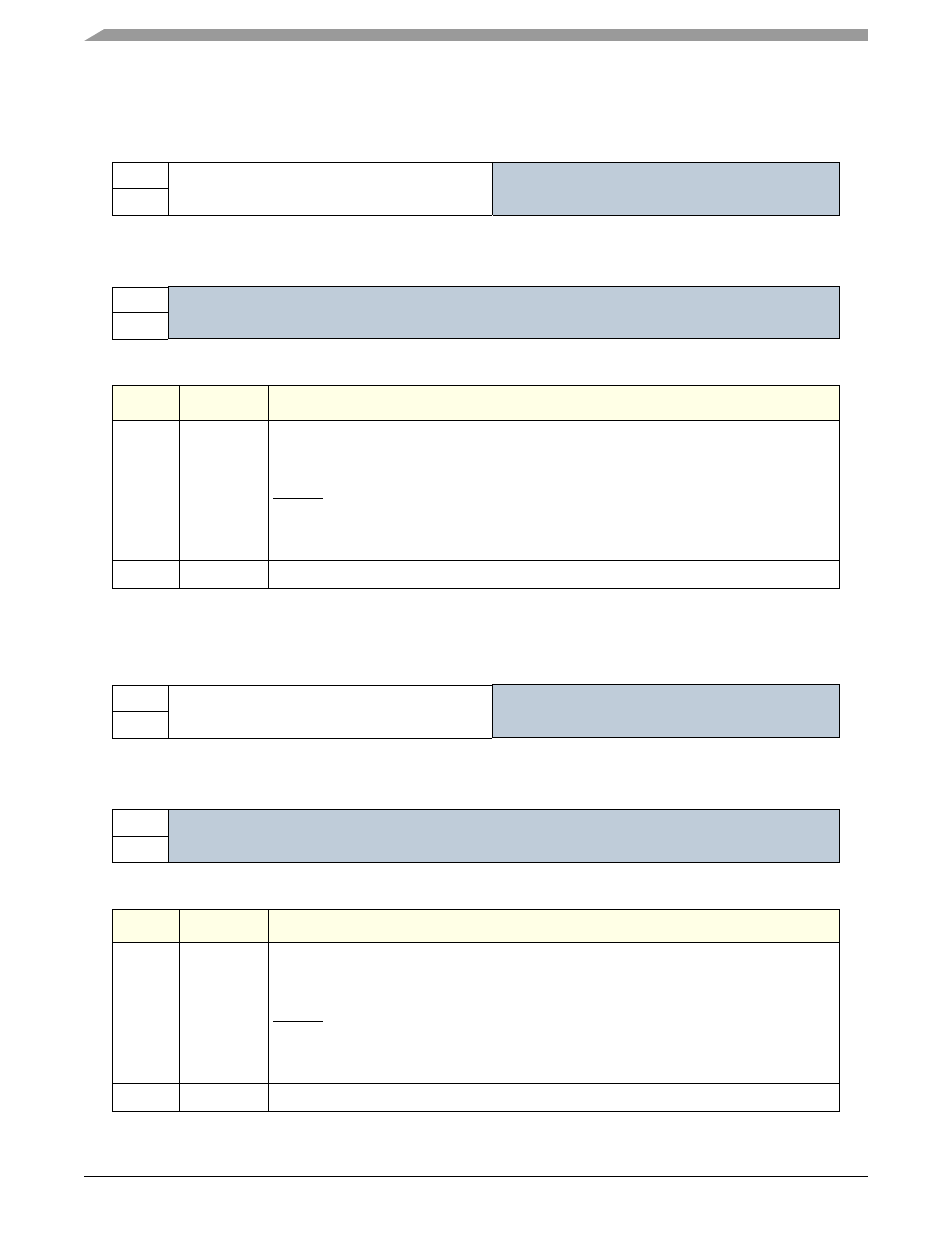

Table 11-26. ATA Drive Cylinder Low Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Data

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:7

Data

Bit content is command dependent. For most commands, this register indicates the data

transfer starting sector number for when CHS addressing is enabled. This register indicates

part of the LBA address when the LBA addressing is enabled.

Register is written only when ATA drive status register bits BSY and DRQ equal 0 and

DMACK is not asserted. If this register is written when BSY and DRQ bits are set to 1, the

result is indeterminate.

Register content is not valid when drive is in sleep mode.

8:31

—

Reserved

Table 11-27. ATA Drive Cylinder High Register

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Data

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Reserved

W

RESET:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:7

Data

Bit content is command dependent. For most commands, this register indicates the data

transfer starting sector number for when CHS addressing is enabled. This register indicates

part of the LBA address when the LBA addressing is enabled.

This register is written only when ATA drive status register bits BSY and DRQ equal 0 and

DMACK is not asserted. If this register is written when BSY and DRQ bits are set to 1, the

result is indeterminate.

Register content is not valid when drive is in sleep mode.

8:31

—

Reserved