5 rx next address pcirnar(r) -mbar + 0x3890, 6 rx last word pcirlwr(r) -mbar + 0x3894 – Freescale Semiconductor MPC5200B User Manual

Page 335

MPC5200B Users Guide, Rev. 1

10-38

Freescale Semiconductor

Registers

10.3.3.2.5

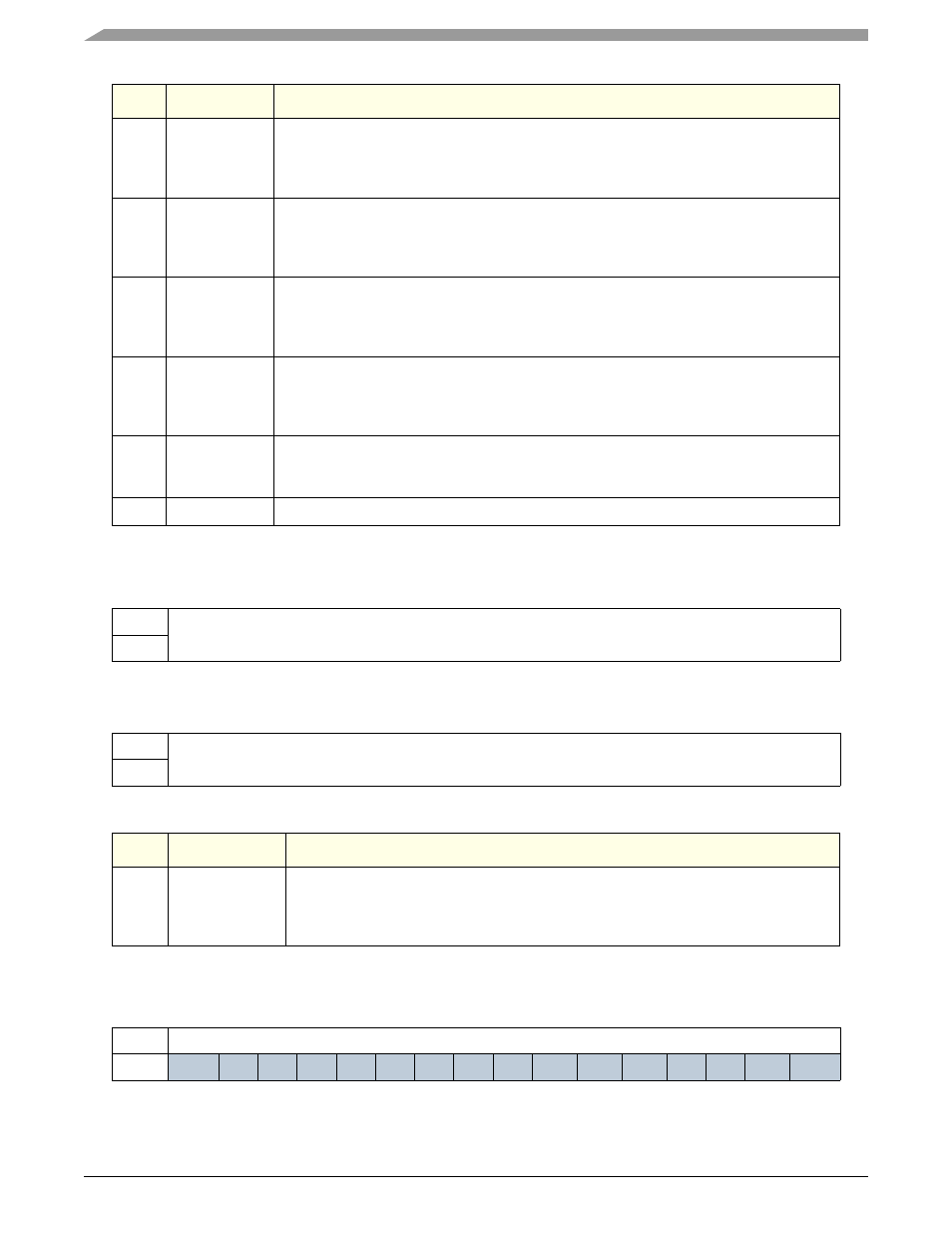

Rx Next Address PCIRNAR(R) —MBAR + 0x3890

10.3.3.2.6

Rx Last Word PCIRLWR(R) —MBAR + 0x3894

11

System error

Enable

(SE)

User writes this bit high to enable CPU Interrupt generation in the case of system error

termination of a packet transmission. It may be desirable to mask CPU interrupts in the case

that Multi-Channel DMA is controlling operation, but in such a case software should be

polling the status bits to prevent a possible lock-up condition.

12

Retry abort

Enable

(RE)

User writes this bit high to enable CPU Interrupt generation in the case of retry abort

termination of a packet transmission. It may be desirable to mask CPU interrupts in the case

that Multi-Channel DMA is controlling operation, but in such a case, software should poll the

status bits to prevent a possible lock-up condition.

13

Target Abort

Enable

(TAE)

User writes this bit high to enable CPU Interrupt generation in the case of target abort

termination of a packet transmission. It may be desirable to mask CPU interrupts in the case

that Multi-Channel DMA is controlling operation, but in such a case software should poll the

status bits to prevent a possible lock-up condition.

14

Initiator Abort

error

Enable

(IAE)

User writes this bit high to enable CPU Interrupt generation in the case of initiator abort error

termination of a packet transmission. It may be desirable to mask CPU interrupts in the case

that Multi-Channel DMA is controlling operation, but in such a case software should poll the

status bits to prevent a possible lock-up condition.

15

Normal

termination

Enable (NE)

User writes this bit high to enable CPU Interrupt generation at the conclusion of a normally

terminated packet transmission. This may or may not be desirable depending on the nature

of program control by Multi-Channel DMA or the processor core.

16:31

Reserved

Unused. Software should write zero to these bits.

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Next_Address

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31 lsb

R

Next_Address

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

0:31

Next_Address

This status register contains the next (unread) PCI address and is updated at the

successful completion of each PCI data beat. It represents a Byte address and is updated

with a user-written Start_Add value when Start_Add is reloaded. This register is intended

to be accurate even if an abnormal PCI bus termination occurs.

msb 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R

Last_Word

W

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description